Philips Semiconductors

TDA9964

12-bit, 3.0 V, 30 Msps analog-to-digital interface for CCD cameras

Objective specification

Rev. 03 — 16 January 2001

13 of 23

9397 750 07918

© Philips Electronics N.V. 2001. All rights reserved.

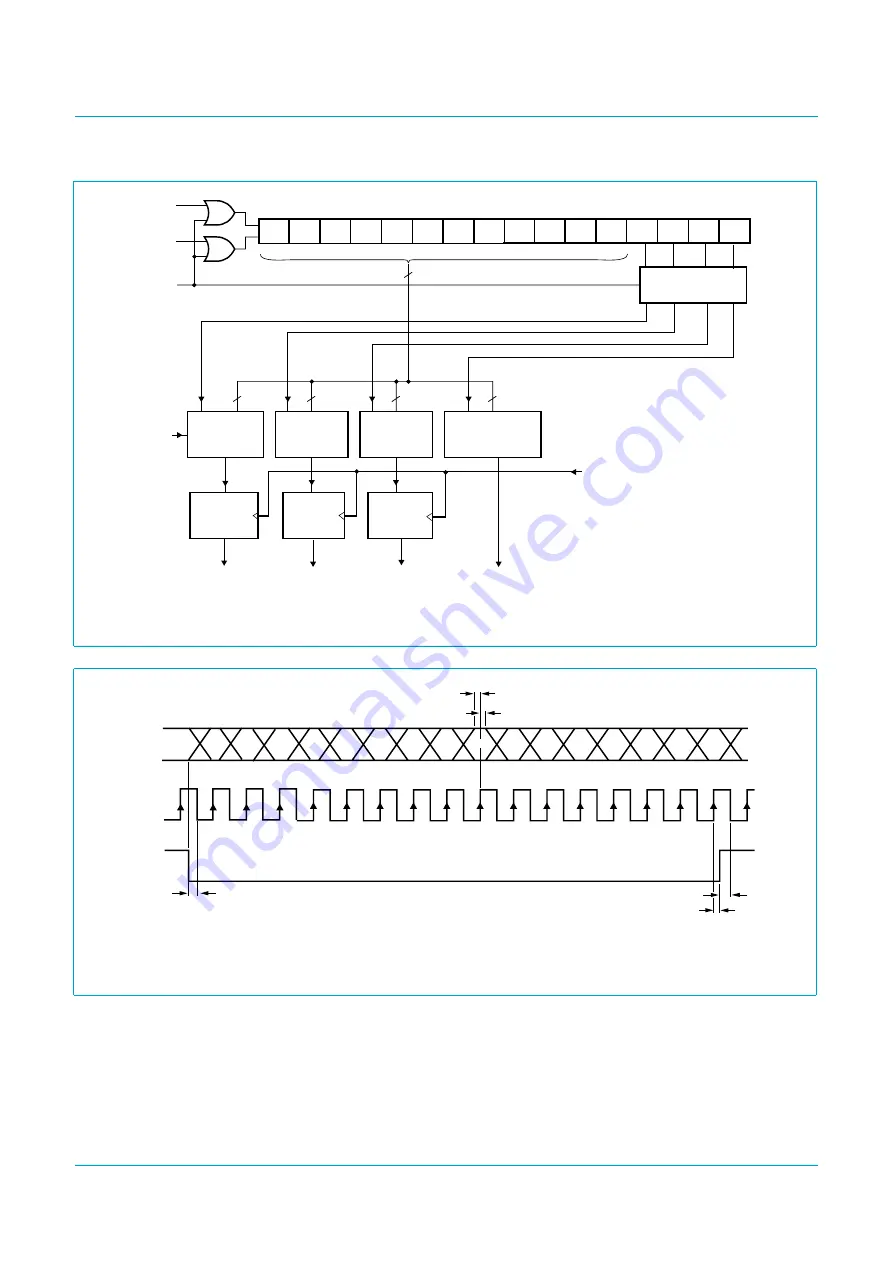

Fig 9.

Serial interface block diagram.

OFDOUT DAC

LATCHES

PGA GAIN

LATCHES

ADC CLAMP

LATCHES

CONTROL PULSE

POLARITY

LATCHES

LATCH

SELECTION

SD0

LSB

MSB

SDATA

SCLK

SEN

SCLK

8-bit DAC

FCE523

PGA control

ADC clamp

control

control pulses

polarity settings

SD2

SD1

SD3

SD4

SD5

12

SD6

SHIFT REGISTER

SD7

SD8

SD9 SD10 SD11

8

8

7

10

A0

A1

A2

A3

VSYNC

FLIP-FLOP

FLIP-FLOP

FLIP-FLOP

t

su1

= t

su2

= t

su3

= 10 ns (min.); t

hd3

= t

hd4

= 10 ns (min.)

Fig 10. Loading sequence of control input data via the serial interface.

FCE524

SDATA

SCLK

SEN

SD11

A1

A2

A3

A0

SD9

SD10

SD7

SD6

SD5

SD4

SD3

MSB

LSB

SD2

SD1

SD0

thd3

tsu3

tsu1

thd4

tsu2

SD8