Philips Semiconductor

s

TD

A9964

12-bit, 3.0 V

, 30 Msps analog-to-digital interface f

or CCD cameras

9397 750 07918

© Philips Electronics N.V

. 2001. All r

ights reser

v

ed.

Objective specification

Re

v

. 03 — 16 Jan

uar

y 2001

3 of 23

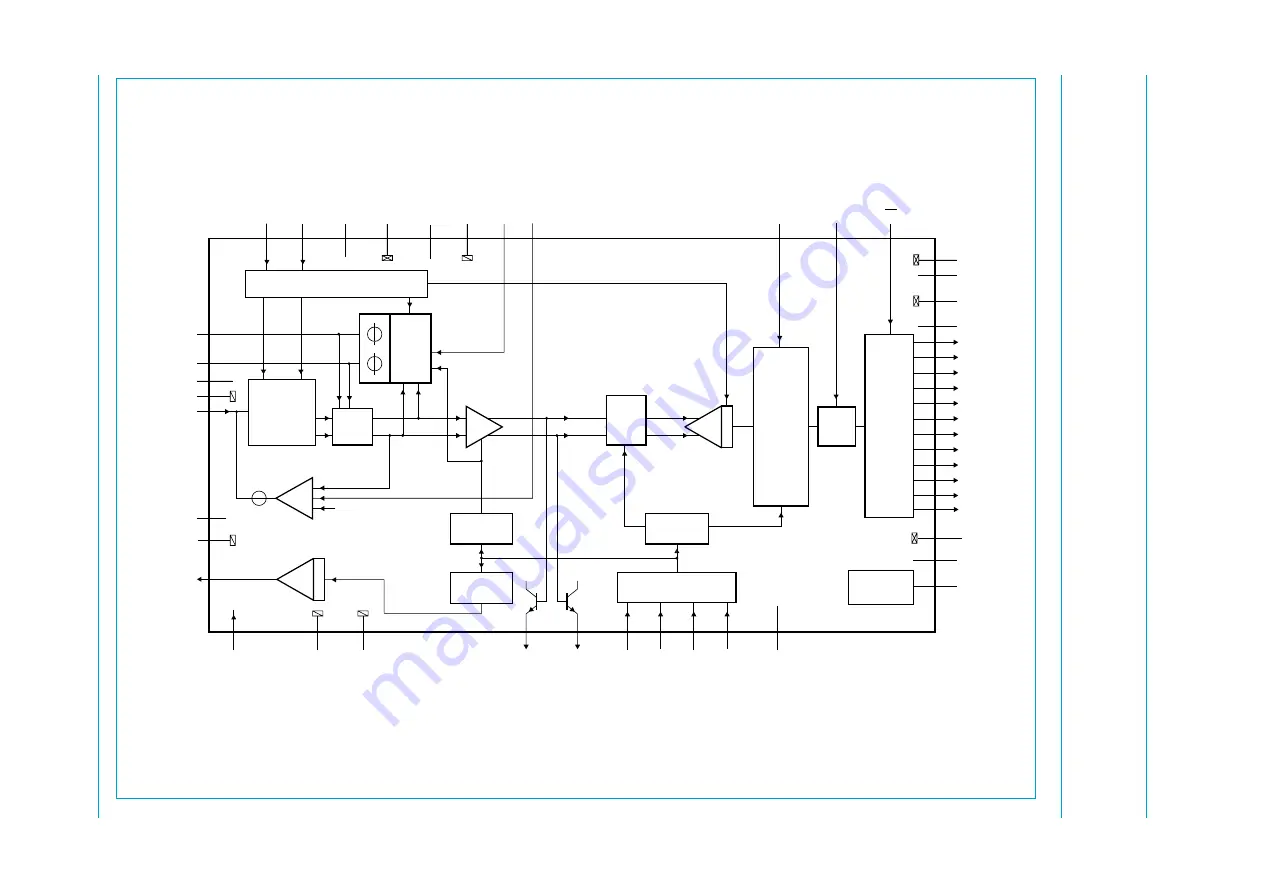

6.

Bloc

k dia

gram

Fig 1.

Block diagram.

FCE515

12-bit ADC

REGULATOR

CDS CLOCK GENERATOR

BLANKING

OUTPUT

BUFFER

37

38

27

26

25

28

29

30

31

32

33

34

35

36

39

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

OGND2

D1

D0

23

24

VCCO1

10

DCLPC

21

VCCD1

VCCO2

22

DGND1

3

AGND2

7

VCCA2

9

CPCDS2

8

CPCDS1

4

IN

5

AGND3

11

OFDOUT

14

VCCA3

OE

43

BLK

47

CLK

40

AGND6

2

AGND1

1

VCCA1

41

VCCA4

48

CLPDM

44

CLPOB

45

SHP

SHIFT

CORRELATED

DOUBLE

SAMPLING

7-BIT

REGISTER

8-BIT

REGISTER

8-BIT

REGISTER

16

15

OPGA

OPGAC

12

6

13

TEST

AGND4

AGND5

46

SHD

SERIAL

INTERFACE

17

18

19

SEN

SCLK SDATA

20

VSYNC

42

STDBY

PGA

CLAMP

Vref

OFD DAC

DATA

FLIP-

FLOP

CLAMP

TDA9964

OGND1

BLACK

LEVEL

SHIFT

hhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhh

hhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhh

hhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhh

hhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhh