Philips Semiconductors

TDA9964

12-bit, 3.0 V, 30 Msps analog-to-digital interface for CCD cameras

Objective specification

Rev. 03 — 16 January 2001

12 of 23

9397 750 07918

© Philips Electronics N.V. 2001. All rights reserved.

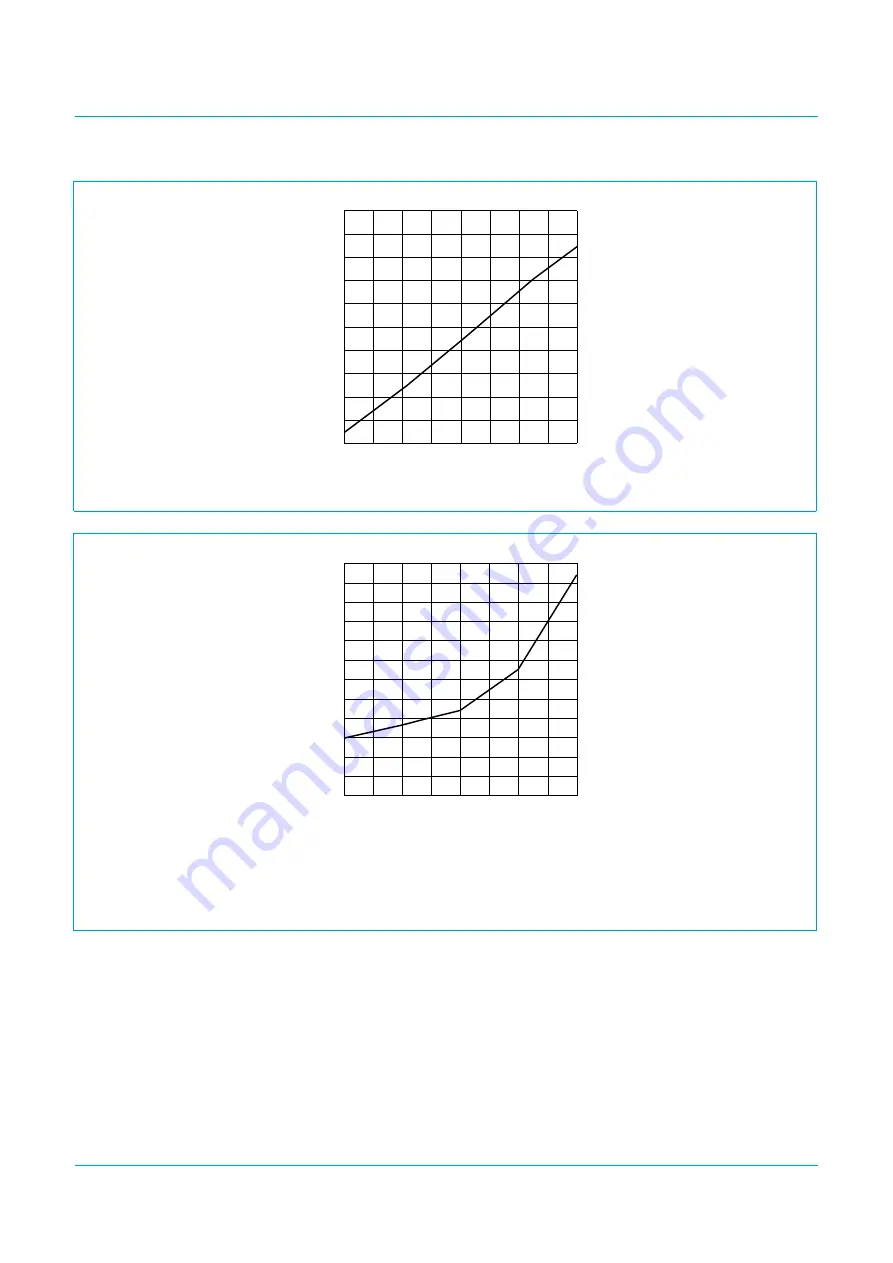

Fig 7.

Total gain from CDS input to ADC input as a function of PGA input code.

0

64

128

255

30

0

1.9

25.9

24

192

PGA input code

TOTAL

gain

(dB)

18

12

6

FCE521

Noise measurement at ADC outputs: Coupling capacitor at input is grounded, so only noise contribution of the front-end is

evaluated. Front-end works at 30 Mpixels with line of 1024 pixels of which the first 40 lines are used to run CLPOB and the

last 40 lines for CLPDM. Data at the ADC outputs is measured during the other pixels. As a result, the standard deviation of the

codes statistic is computed, resulting in the noise. No quantization noise is taken into account as there is no input.

Fig 8.

Typical total noise performance as a function of PGA gain.

handbook, halfpage

0

64

128

255

6

0

4

5

192

PGA code

Ntot(rms)

(LSB)

3

2

1

FCE522