9397 750 13022

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data sheet

Rev. 02 — 26 April 2004

11 of 27

Philips Semiconductors

TEA5880TS

Integrated FM stereo radio IC for host processor tuning

[1]

The frequency is decreased when increasing the content of this register (more capacitors).

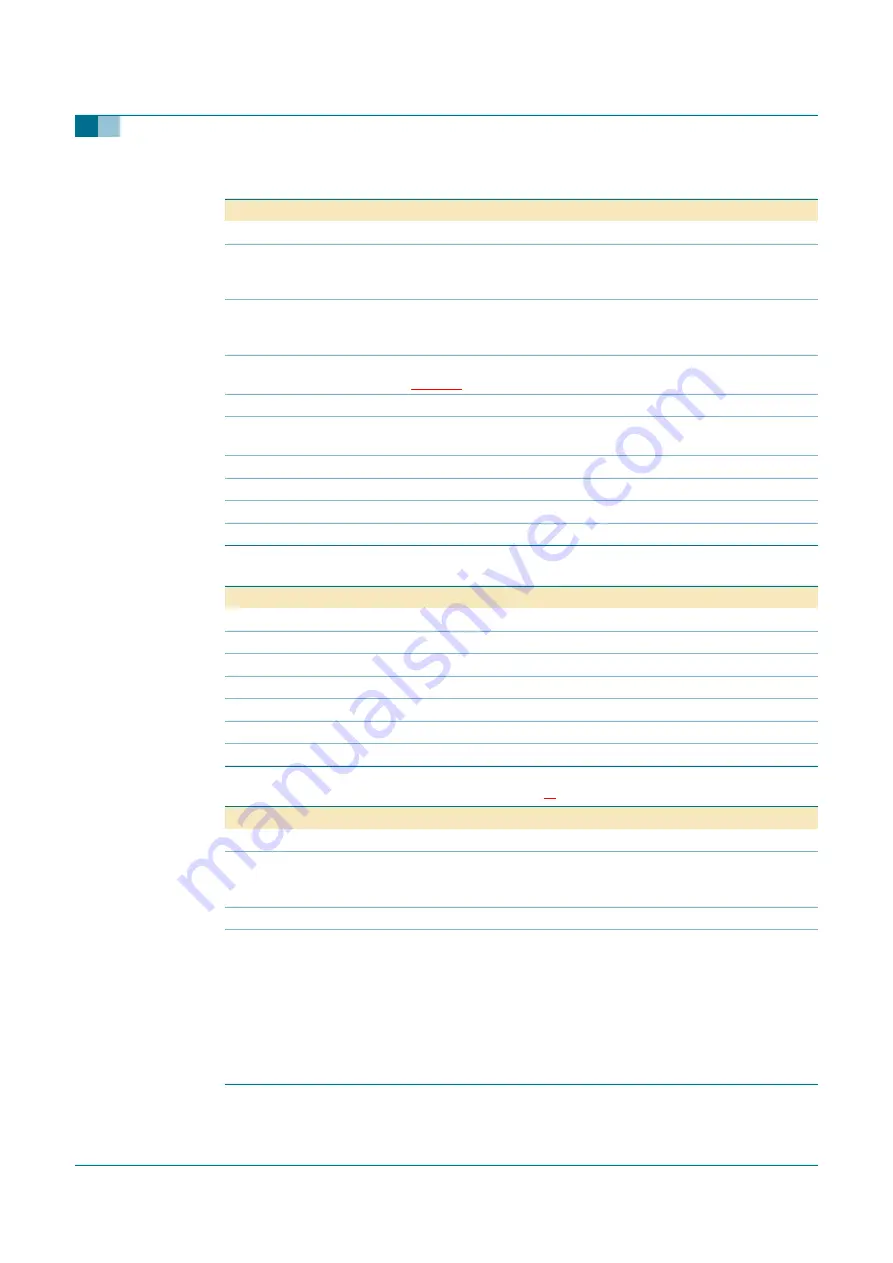

Table 12:

CTRL_B - (address 4h) bit description

Bit

Symbol

Description

14 to 11 -

address bits

10

L_CNT

latch counter: a transition from logic 1 to logic 0 will latch the

COUNTER register into the PISO (reading the PISO hereafter will read

the COUNTER register)

9

L_STS

latch status: a transition from logic 1 to logic 0 will latch the STATUS

register into the PISO (reading the PISO hereafter will read the STATUS

register)

8 to 6

-

reserved for output level control; should be written with 4 (100b);

see

5

DEEMP

de-emphasis: logic 1 is 75

µ

s (USA), logic 0 is 50

µ

s (Europe, Japan)

4

PISO_CLR

a transition from logic 1 to logic 0 will clear the PISO; the PISO should

be clear before reading the STATUS/COUNTER register

3

CNT_RST

a transition from logic 1 to logic 0 will clear both counter 1 and counter 2

2

CNT1_EN

counter 1 enabled (counting mode) when set to logic 1

1

-

should be written to logic 0

0

MONO

mono mode when set to logic 1, stereo mode when set to logic 0

Table 13:

Description of output level control register bits

Value

Decimal

Output level

0000b

0

12 mV

0001b

1

20 mV

0010b

2

35 mV

0011b

3

60 mV

0100b

4

100 mV

0101b

5

170 mV

0110b

6

200 mV

Table 14:

CAP_FM - (address 5h) bit description

Bit

Symbol

Description

14 to 11 -

address bits

10

-

reserved for capacitor extra current; this bit should be written to logic 1

by any access to the CAP_FM to ensure that the device functions

properly

9 to 8

-

reserved, should be written to logic 0

7 to 0

FC[7:0]

FM capacitor bank switches for adjusting the FM (RF) frequency in big

steps. Every bit, when set, will switch on a capacitor with a weight

according to its position i.e. bit 0 has weight 1, bit 1 has weight 2, bit 2

has weight 4 etc, bit 6 has weight 64, except for bit 7, which also has the

same weight as bit 6; there is thus only 7

1

⁄

2

effective bits; this means

that the value range 0 to 127 will switch on different capacitors the value

range 128 to 191 switches on the same capacitors as range 64 to 127,

the value range 192 to 255 will switch on different capacitors (an

overlapped range of 64 values caused when FC[7:6] = 01b or 10b)