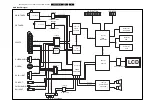

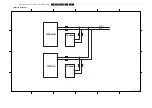

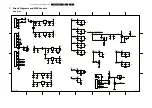

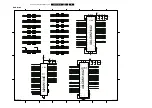

Circuit Diagrams and PWB Layouts

21

TES1.0E LA

7.

Main Board

1

2

3

4

5

6

7

8

A

B

C

D

8

7

6

5

4

3

2

1

D

C

B

A

TIXN0

51

TIXN1

52

TIXN2

54

TIXN

3

55

TIXN4

56

TIXN5

2

TIXN6

3

TIXN7

4

TIXN

8

6

TIXN9

7

TIXN10

8

TIXN11

10

TIXN12

11

TIXN1

3

12

TIXN14

14

TIXN15

15

TIXN16

16

TIXN17

1

8

TIXN1

8

19

TIXN19

20

TIXN20

22

TIXN21

2

3

TIXN22

24

TIXN2

3

25

TIXN24

27

TIXN25

2

8

TIXN26

3

0

TIXN27

50

TXCLKIN

3

1

PLLGND

3

5

PLLGND

33

GND

5

GND

1

3

GND

21

GND

29

GND

5

3

LVGND

3

6

LVGND

49

LVGND

4

3

VCC

1

VCC

9

VCC

26

LVVCC

44

PLVCC

3

4

TXOUT0-

4

8

47

45

TXOUT1-

46

TXOUT2-

42

41

TXOUT

3

+

3

7

TXOUT

3

-

38

TCLKOUT-

40

3

9

-PWRDWN

3

2

R_FB

17

U904

D

S

90C

38

5

1

2

3

4

5

6

7

8

9

10

11

12

1

3

14

15

16

17

1

8

19

20

S

905

CON20

R0

R1

R2

R

3

R4

R5

R6

R7

G0

G1

G2

G

3

G4

G5

G6

G7

B0

B1

B2

B

3

B4

B5

B6

B7

PWRD

L911

BEAD

L912

BEAD

C900

100nF

C906

100nF

C924

10

u

F

C9

33

10

u

F

R900

0R

R904

120R

R90

3

120R

3

.

3

V

3

.

3

V

3

.

3

V

RIN0-

RIN1-

RIN2-

RIN

3

-

RCLK-

RCLK+

RIN0+

RIN1+

RIN2+

RIN

3

+

V_TFT

RIN0-

RIN1-

RIN2-

RIN

3

-

RCLK-

RCLK+

RIN0+

RIN1+

RIN2+

RIN

3

+

1

2

3

4

5

6

7

8

9

10

11

12

1

3

14

15

16

17

1

8

19

20

21

22

2

3

24

25

26

27

2

8

29

3

0

S

90

3

CON2X15

L914

BEAD (LG)

L91

3

BEAD (LG h

a

riç)

R901

0R

R906

R

R902

0R

BL_ON/OFF

R905

R

V_TFT

V_TFT

RIN0-

RIN1-

RIN2-

RIN

3

-

RCLK-

RCLK+

RIN0+

RIN1+

RIN2+

RIN

3

+

3

.

3

V

S

R907

R

R90

8

R

LVD

S

OPTION

1

2

3

4

5

6

7

8

RN90

120R

1

2

3

4

5

6

7

8

RN91

120R

ADE_CLK

ADE_DE

ADE_H

S

YNC

ADE_V

S

YNC

R909

0R

R911

0R

R910

0R

R91

3

0R

R912 0R

C951

2200

u

F

R914

0R

R27

3

N

S

R272 N

S

OD

S

EL1

1

2

3

4

5

6

7

S

101

S

HARP CONTROL

3

.

3

V

R2

8

0

0R

OD

S

EL1

R2

8

1

0R

R279

0R

R19

8

0R

R144

0R

3

.

3

V

R199

0R

3

.

3

V

R145

0R

3

.

3

V

R14

3

0R

R915

0R

TP1

83

TP1

8

4

TP1

8

5

TP1

8

6

TP1

8

7

TP1

88

5

6

7

8

1

2

3

4

L1

33

RN - FERRIT

5

6

7

8

1

2

3

4

L1

3

4

RN - FERRIT

G_16510_027.ep

s

201106

05TA059A