36

TES1.0E LA

7.

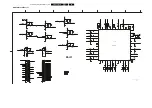

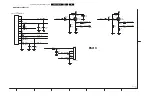

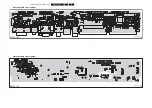

Circuit Diagrams and PWB Layouts

Side I/O Board

1

2

4

3

A

B

C

D

4

3

2

1

D

C

B

A

L107

BEAD

AV_CVB

S

C115

1nF

L110

BEAD

C111

10pF

R102

15K

AV_L

C109

1nF

C11

3

1nF

L111

BEAD

R10

3

15K

AV_R

C110

1nF

C114

1nF

C116

1nF

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

1

2

3

S

100

HEADF GND

GND

L

R

AGND

L100

22

u

H

L101

22

u

H

C100

220nF

GND

C101

220nF

GND

C102

100nF

GND

C10

3

100nF

GND

R100

4.7R

C104

10nF

GND

R101

4.7R

C105

10nF

GND

FD1 FD2 FD

3

1

2

3

S

101

CON

3

1

2

3

4

5

S

10

3

CON5

5

4

3

2

1

6

S

102

CHINC

3

G_16510_046.ep

s

211106

05TA051D