Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 52

TES1.0E LA

9.

9.5.3

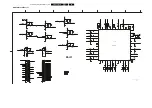

Multistandard TV / VCR Digital Video Decoder and Output Scaler, STV2310 (U100)

Figure 9-5 Internal block diagram and pin configuration of the Video Decoder

Block Dia

g

ram

Pin Confi

g

uration

G_16510_06

3

.ep

s

221106

Fully Automatic

PAL/NTSC/SECAM

Decoder

Data Slicer

(TxT, CC, ...)

Adaptive

Luminance Delay

R/Cr

CVBS1/Y

CVBS2/Y

C

YCrCb[7:0]

HSYNC

Data Selection

and Output Interface

Line

Format

Converter

and

Output

Scaler

Analog to

Digital

Conversion

Analog to

Digital

Conversion

and SRC

Cr Cb

Tint

Control

Luma

Chroma

Separator

Synchronization

and IC Monitoring

Clock

VSYNC

Field

G

B/Cb

STV2310

YCRC

B

5

YCRC

B

4

V

SS_IO

VDD3

3

_

IO

YCRC

B

3

YCRC

B

2

YCRC

B

1

YCRC

B0

VDD1

8

_

OUT

VSS_OUT

CL

K_

D

A

T

A

PLL

L

OCK

VDD1

8

_

CORE

VSS

YCRC

B

7

YCRC

B

6

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

17 18 19 20 21 22 23 24

29 30 31 32

25 26 27 28

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

VSS

TST_MODE

VDD18_CORE

VSS

SDA

SCL

VDD18_CORE

VSS

NRESET

VDD33_IO

VSS_IO

I2CADD

VCC18_CVBS

CVBS2_Y

C

VDD18_CORE

CLKSEL

CLKXTM

XTALIN_CLKXTP

XTALOUT

GND_CLK

VCC18_CLK

VCC18SUB

GNDSUB

VCC33SUB

FIELD

VSYNC

HSYNC

REFM_RGB

REFP_RGB

FB

SHIELD

VI

DEO_

O

UT

VI

DEOCOM

M

ADCIN

VCC3

3

_

IO

GND_

IO

GND_

DIG

VCC1

8

_

DIG

B_CB

G

R_

CR

GND_

RGB

VCC1

8

_

RGB

GND_

CVBS

CVBS1_

Y

REFM

_CVBS

REFP_

C

VBS