Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 53

TES1.0E LA

9.

9.5.4

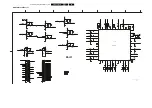

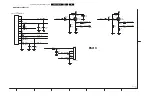

Main Tuner, UV1316 Mk4 (T100)

Figure 9-6 Internal block diagram and Pin configuration of the main tuner

Block Dia

g

ram

Pin Confi

g

uration

G_16510_060.ep

s

221106

SYMBOL

PIN

DESCRIPTION

AGC

1

Automatic Gain Control Voltage

TU

2

Tuning voltage monitor (output)

AS

3

I

2

C-Bus Address Select

SCL

4

I

2

C-Bus Serial Clock

SDA

5

I

2

C-Bus Serial Data

n.c.

6

Not Connected

V

s

7

Supply V5V

ADC

8

ADC Input

(5)

V

ST

9

Fixed tuning Supply V33V

I.F out 2 / d.n.c

10

Symmetrical I.F output 2 / Do not connect for asymmetrical

I.F out 1

11

Asymmetrical I.F Output / Symmetrical I.F output 1

GND

M1,M2,M3,M4 Mounting Tags (Ground)

AGC

TU

AS

SCL

SDA

n.c

5V

ADC

33V

IF2/nc

IF1

HIGH

5V

MID

5V

LOW

5V

PLL

1

IF2

nc

IF1