Circuit Descriptions, Abbreviation List, and IC Data Sheets

9.

9.4.5

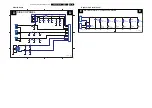

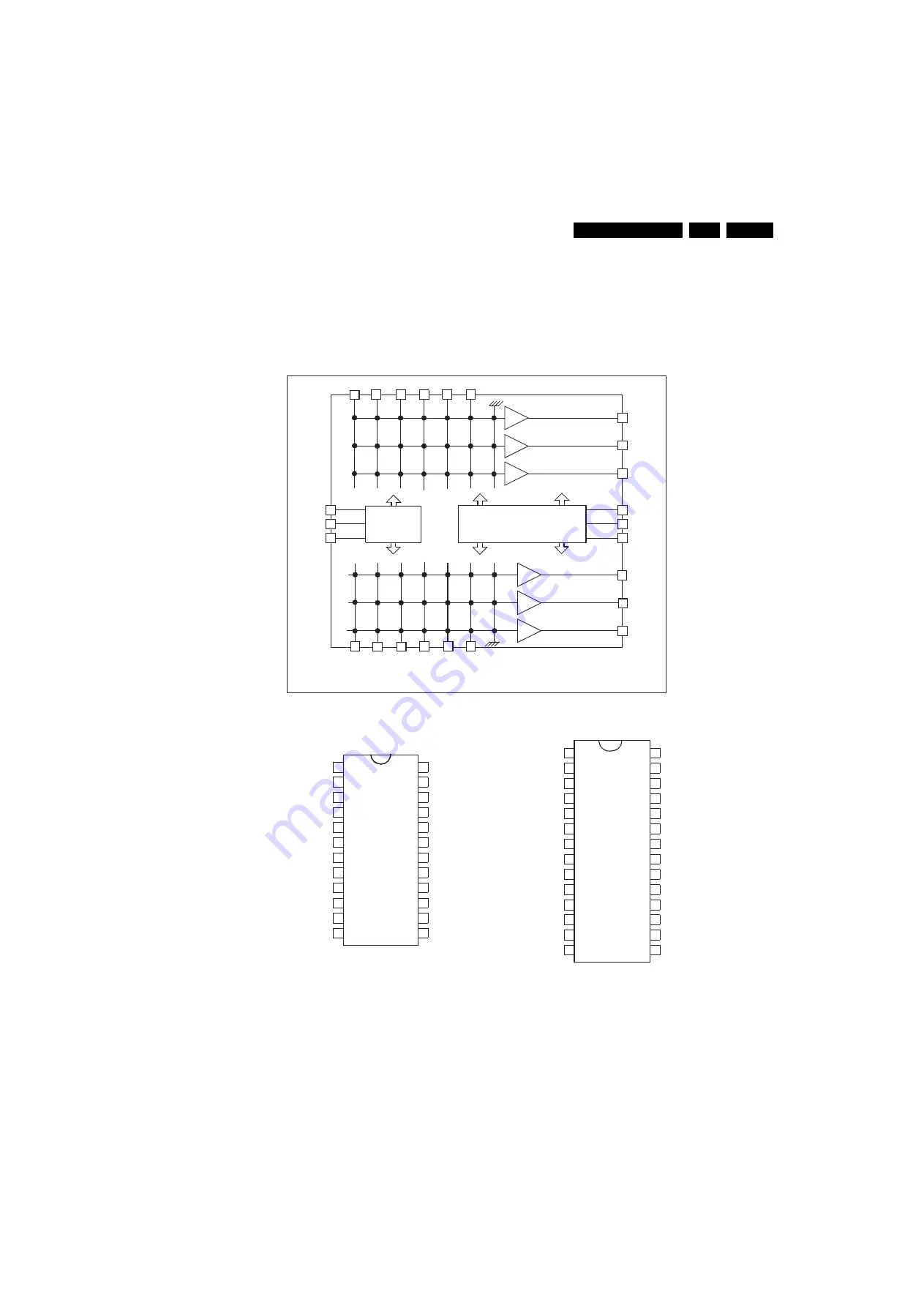

Bus-controlled Audio Matrix, TEA6422 (U13)

Figure 9-5 Internal block diagram and pin configuration

PIN CONFIGURATION

BLOCK DIAGRAM TEA6422

H_17490_0

3

1.ep

s

291007

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

24

23

22

21

11

12

GND

CAPACITANCE

L1

L2

L3

L4

L5

LOUT1

ROUT1

SDA

SCL

ADDR

R1

R2

R3

R4

R5

V

S

L6

LOUT2

R6

ROUT3

LOUT3

ROUT2

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

24

23

22

21

11

12

25

13

14

28

27

26

SDA

SCL

ADDR

R1

R2

R3

NC

NC

R4

R5

R6

ROUT3

LOUT3

ROUT2

LOUT2

ROUT1

LOUT1

L6

L5

L4

NC

NC

L3

L2

L1

GND

CAPACITANCE

V

S

SDIP24

SO28

RIGHT INPUTS

GAIN = 0 dB

RIGHT

OUTPUTS

SDA

SCL

ADDR

LEFT

OUTPUTS

LEFT INPUTS

BUS DECODER

SUPPLY

GAIN = 0 dB

V

S

C

GND