Circuit descriptions and List of abbreviations

GB 100

VR120

9.

9.3.3

CMT detection (video detection with CSYNC)

This has been extended due to identification problems with

weak transmission signals and video signals not conforming

to the STANDARD (common channel interference). The

CSYNC line is supplied to the

µ

P [7899-B] on pin 50. A

hardware integration [7807,7808,7809] of the video pulse

compensates the interference generated by the common

channels and weak signals.

9.3.4

EE-PROM

The EE-PROM [7818] is a non-volatile memory which can be

erased and written to electrically. (Data remains even if the

operating voltage fails). Data specific to the device such as

the X distance, head changeover position, preset stations,

optional bytes etc. is stored in the EE-PROM [7818]. The

data is accessed by the

µ

P via the I

2

C bus.

9.3.5

Easy link (P50)

For the communication between the TV set, video recorder

and the peripheral devices, a bi-directional single-wire bus is

used, which runs via pin 10 to scart socket 1.

The output signal is generated on pin 84 of the

µ

C [7899-B],

pin 68 is the signal input.

9.3.6

Shuttle

The shuttle is connected to the motherboard on plug

pos.1982. It is a binary coded rotary switch with a rotation

angle of +/- 70 degrees and 16 switch positions. These are

input and evaluated via four lines (shuttle b1 - shuttle b4) to

the input ports P24 - P27 [7899B pins 2-5].

9.3.7

Satmouse

For activating a sat-receiver via an external infrared

electronic transmission unit (Satmouse) a bi-directional data

line, a short-circuit proof +5V and earth are provided via a 3-

pin 3.5mm jack [1941].

The +5V is limited to approx. 140 mA using a current limiting

switch [7812 and peripherals].

9.4

Deck electronics DE (DE part)

The deck interface IC MP63100FP [7463] contains the

following functional groups:

•

CTL stage (tape synchronisation)

•

Sensor interface

•

Power on reset

•

Head drum motor driver

•

Loading motor driver

•

Capstan motor control

9.4.1

CTL stage

The IC M63100FP [7463] contains a read/write stage for the

CTL track with the option of overwriting an existing CTL track

without any interference. The playback stage is fitted with a

“digital” five-stage AGC. This logic circuit identifies the size of

the output signal supplied by the CTL head, and then selects

the best amplification ratio in the playback stage using

comparators.

The CTL head voltage can therefore vary greatly, if V

max

/

V

min

is great. The slowest tape speed is in LP mode. The

fastest speed is adjusted during rewind. To ensure that the

duty cycle in the tape sync is always reproduced correctly in

the conditions mentioned above (important for detecting

VISS marks), the amplifier must not be overdriven.

The five-stage AGC alone cannot cover the large dynamic

range of the input voltage. The amplifier is therefore also

equipped with a low pass characteristic (fg = 3kHz typ.;

internal).

In parallel with the CTL head is the RC cell comprising

capacitor [2479] and resistor [3471]. The capacitor [2479],

together with the CTL head inductivity, causes a resonance

step-up at around 10 kHz and the resistor [3471] suppresses

this step-up. This creates an aperiodic transient response in

the resonance. Beyond the resonance frequency, there is an

adjustment in terms of a steep fall in the frequency

transmission characteristic. This effectively suppresses high-

frequency pick-ups. The CTL head signal amplitude in

standard play is around 1mVp (typ.) which means that the

amplification for the playback amplifier must be

correspondingly high. To avoid offset problems, a 100 F

electrolytic capacitor [2490] is fitted in the negative feedback

branch for DC decoupling.

The polarity of the playback amplifier can be changed using

the Video Index Search System (VISS) voltage. This is the

only way in which the P can write a VISS mark on the tape

without spikes. The Write/Read (W/R) signal is used to

switch over between record and playback:

W = “H“, R = “L“.

9.4.2

Power on reset (POR) generator

The POR generator contained in the M63100FP [7463]

requires only one external capacitor [2477], which specifies

the length of the POR pulse. For 33 nF, t

POR

is approx. 30ms.

The response threshold of the reset circuit is between 4.5

and 4.8 V. Supply fluctuations which are shorter than tPOR/

100 area and which do not fall below 4.0 V, do not trigger the

POR. The P is reset using the inverted POR.

9.4.3

The sensor interface :

The four comparators in the M63100FP [7463] are used to

convert sensor signals to the logic level. The outputs are

overload protected by a current limiter and thermal overload

protection. Only the non-inverting input on each comparator

is accessible from the outside. The other inputs are

connected to an internal reference of 2.5V. The fixed

hysteresis of the comparators of approx. 18 mV is also

located internally.

The comparators are connected as follows:

Comparator 1: In = FTA, pin 39; Out = FTAD, pin 34:

FTA = threading tachometer. This signal comes from a forked

light barrier in the deck. An infra-red light beam is interrupted

by a 4-blade impeller (butterfly). The output amplitude for the

light barriers should be less than 2V for the low level and

greater than 3V in the high level to ensure a correct

evaluation process. An additional hysteresis is created with a

resistor [3476]. For unit versions <1W and FOME the

external operation amplifier [7530B] is used to reduce the

power consumption in <1W mode.

Comparator 2: In = WTR, pin 38; Out = WTRD, pin 33:

WTR = Winding tachometer right, from a reflection

photoelectric barrier. The level is the same as for the FTA.

Comparator 3: In = WTL, pin 37; Out = WTLD, pin 31 :

WTL = Winding tachometer left, from a reflection

photoelectric barrier. The level is the same as for the FTA.

Summary of Contents for VR570

Page 12: ...Direction for use GB 12 VR120 3 3 Direction for use RT111 RT116 RT112 RT114 RT123 RT121 RT128 ...

Page 15: ...Direction for use GB 15 VR120 3 SAT VR870L VR870CC VR720 Set width 435 mm ...

Page 56: ...Service modes Repair tips GB 56 VR120 5 Engineer s remarks ...

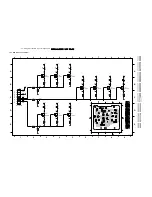

Page 79: ...Circuit diagrams and PWB layouts Wiring diagram 79 VR120 7 7 16 Wiring Diagram Motherboard ...

Page 81: ...Circuit diagrams and PWB layouts Wiring diagram 81 VR120 7 Engineer s remarks ...

Page 82: ...82 VR120 7 Circuit diagrams and PWB layouts Wiring diagram Engineer s remarks ...

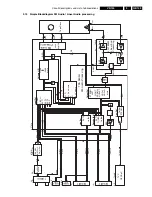

Page 83: ...Circuit diagrams and PWB layouts Wiring diagram 83 VR120 7 7 18 Mother board component side ...

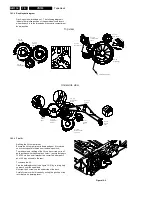

Page 119: ...Tape deck GB 119 VR120 10 ...

Page 123: ...Tape deck GB 123 VR120 10 Engineer s remarks ...