Circuit descriptions and List of abbreviations

GB 101

VR120

9.

Comparator 4: In = FG, pin 35; Out = FGD, pin 30:

FG = capstan tachometer. This signal stems from an

amplifier for the tachometer hall sensor on the motor unit

[1946 pin 4]. The output impedance is 10 kOhm. The

amplitude of the virtually sinusoidal signal is normally 1 Vp. It

should not fall below 300 mVpp. It is AC-coupled via a

capacitor [2485]. In order for a bias current to flow, the input

pin 31 must be passed via a resistor [3474] to the reference

voltage on pin 4. A capacitor [2480] for filtering out high-

frequency interference is arranged in parallel to the bias

resistor.

9.4.4

Interface to the head drum motor driver part

The head drum control voltage (speed and phase control

information) is output via a P-output (7899-B pin 35; PWM

14-bit). This pulse-wide modulated signal is fed to the motor

driver IC M63100FP [7463 pin 11] and integrated with the

capacitor [2469]. This IC already has a completely integrated

‘start-up’ circuit fitted. For the commutation, the head drum

motor driver uses the e.m.f. on the non-current carrying

motor coil (transformer principle). The motor speed is also

discharged from there at the same time. The phase of the

head disc is discharged from a position coil. The speed and

phase are multiplexed into one signal [7463 pin 6] and

output, which means that the falling edge of the signal is

available with a positive edge for the speed (FG/450Hz) and

at 25Hz for the position pulse (PG).

The motor driver M63100FP [7463] is connected to the head

drum motor on the motherboard using plug [1948].

•

DRUM

is the speed-phase control signal.

The resolution is 14 bit.

•

PG/FG

is the combined POS/tachometer

signal from the M63100FP [7463].

9.4.5

Interface to the loading motor driver part:

The loading motor driver part is constructed for use as a

bridged dual power operations amplifier (OPAMP). It can

supply max. +/-0.8A output current. The output current is

limited to approx. 0.7A by the internal resistance of the

loading motor (18 Ohm typ.) (start-up or motor is blocked).

Between the IC outputs [7463, pins 22 and 24] there is a

“Boucherot” circuit [3467] 1E, [2474] 100 nF for suppressing

a spurious 3MHz oscillation from the output stage. One half

of the bridge is controlled via the TMO line on pin 27 and acts

as a comparator. The other half is an amplifier integrator with

a 3.9 gain. A change in the input voltage (THIO) of between

0 and 5V on pin 25 results in a change in the output voltage

of between 0V and almost Ub. With 50% modulation (THIO =

2.5 V) pin 24 has approx. 7 V. The 100nF capacitor [2473] in

the negative feedback of the op-amp filters out the PWM

frequency of approx. 39kHz. During POR, the P issues “L” to

the THIO line, whilst TMO is “H”. This ensures that no current

flows in the motor for the duration of the POR pulse. This

prevents the motor being destroyed in case of prolonged

running or blockage. This arrangement also has a

disadvantage, however. This is that if the 5 V supply fails

(e.g. because the 5V fuse has blown), residual voltages may

be passed to the IC inputs via the adjacent 14 V voltages.

These residual voltages trigger the comparator and the op-

amp in opposite ways, causing a short-circuit in the blocked

loading motor after about a minute. To get around this

problem, a separate voltage divider is used internally for the

comparator. Both outputs on the M63100FP [7463] are then

in “common mode” if this error occurs.

9.4.6

Interface to the capstan motor

The driver IC on the capstan motor is activated via connector

[1946].

CAP is the signal for the capstan speed. This voltage may

vary without load between 0 and 5 V.

The rotational direction of the motor is determined using

CREV (capstan reverse). The maximum current input for the

motor is limited to 1A. Typical values in PLAY mode are 0.2

... 0.3 A.

9.5

Front end FV (FV part)

9.5.1

The front end comprises the following parts :

•

TUMOD = Tuner (+ Modulator Option) (+Booster Option)

(+Passive Loop Through Option)

•

IF amplifier & video demodulator IC TDA 9817, [7705]

with FM - PLL demodulator

•

IF amplifier & video demodulator IC TDA 9818, [7705]

with FM - PLL and AM demodulator

•

FM stereo decoder TDA 9873 [7760]

•

Multi-standard FM stereo, AM, NICAM decoder

MSP3415D [7761]

9.5.2

The front end has been designed to receive the following

systems:

•

PAL B/G with FM stereo

•

PAL 1 or PAL BG with NICAM stereo

•

PAL BG with NICAM and FM stereo

•

PAL BG/I SECAM L/L’ with NICAM and FM stereo

•

PAL BG SECAM DK with NICAM and FM stereo

•

PAL B/G

= /01,/02/16

•

PAL I

= /05 Pal I with UHF reception

•

PAL I Ireland

= /07 Pal I with VHF/UHF reception

•

SECAM L,L‘, PAL BG/I = /39

•

PAL B/G, PAL I, SECAM D/K = /55

•

PAL B/G, SECAM DK = /58

The relevant layout is given in the version list on the circuit

diagram.

9.5.3

Tuner modulator (TUMOD)

The tuner and modulator are fitted into the same housing.

Both the tuner and the modulator are PLL-controlled. The

reception frequency or modulator frequency is set using the

IIC bus.

The amplification is determined by the AGC voltage at pin 5

[1701] (for operation, see IF demodulator section).

9.5.4

IF selection

The IF frequency of the video carrier is 38.9 MHz for all

systems except SECAM L’ (33.9 MHz).

For PAL BG-SECAM DK and for PAL BG/I-SECAM L/L´ a

quasi-split audio system is used; i.e. for video and audio

carriers, separate surface-wave filters (OFW) are required

[1704, 1703]. For all other standards an intercarrier system is

used; i.e. a common OFW with audio stair-step can be used

[1704] for video and audio carriers.

For the PAL BG/I-SECAM L/L’ version, an additional circuit

for suppressing the adjacent channel audio carrier is

provided, which is set using coil [5704] to maximum

suppression at 40.4MHz.

9.5.5

IF demodulator

TDA 9818

The IF signal from the tuner is processed by another

demodulator IC of type TDA 9818 [7705]. The TDA 9818 is

Summary of Contents for VR570

Page 12: ...Direction for use GB 12 VR120 3 3 Direction for use RT111 RT116 RT112 RT114 RT123 RT121 RT128 ...

Page 15: ...Direction for use GB 15 VR120 3 SAT VR870L VR870CC VR720 Set width 435 mm ...

Page 56: ...Service modes Repair tips GB 56 VR120 5 Engineer s remarks ...

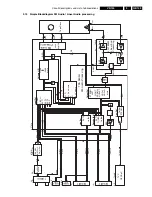

Page 79: ...Circuit diagrams and PWB layouts Wiring diagram 79 VR120 7 7 16 Wiring Diagram Motherboard ...

Page 81: ...Circuit diagrams and PWB layouts Wiring diagram 81 VR120 7 Engineer s remarks ...

Page 82: ...82 VR120 7 Circuit diagrams and PWB layouts Wiring diagram Engineer s remarks ...

Page 83: ...Circuit diagrams and PWB layouts Wiring diagram 83 VR120 7 7 18 Mother board component side ...

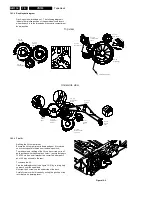

Page 119: ...Tape deck GB 119 VR120 10 ...

Page 123: ...Tape deck GB 123 VR120 10 Engineer s remarks ...