Circuit descriptions and List of abbreviations

GB 102

VR120

9.

used to demodulate pos. or neg. modulated video carriers. It

is possible to generate a QSS-audio-IF signal or an

intercarrier IF signal for demodulation in the audio

demodulator [7761]. For the best possible video signal

performance the IF signal is conveyed via an OFW [1704]

according to the standard. The audio-IF carrier is selected in

the audio OFW [1703] which is switched for SECAM L’. The

output signal for this OFW is further processed in the TDA

9818. FM carriers are converted from the IF level into the

audio IF position and further processed in the audio

demodulator. The AFC coil [5702] on the TDA 9818 is

adjusted so that when a frequency of 38.9 MHz is supplied to

the IF output of the tuner, the AFC voltage on pin 17 on the

TDA 9818 is 2.5V. The setting of the picture carrier frequency

for SECAM L in the TDA 9818 is achieved by connecting pin

7 of the IC via a potentiometer [3730] to earth. The AFC

voltage on pin 17 TDA 9818 should then also be 2.5V at 33.9

MHz. The HF-AGC is set using the AGC controller [3707] so

that with a sufficiently large input signal (74 dBV), the voltage

at the IF output on the tuner [1701, pin 17] is 550 mVpp. The

setting must be carried out when the audio carrier is switched

off. The demodulated video signal appears on pin 16 [7705].

The video drop [1705] reduces adjacent channel sound

carrier and sound carrier remainders in the video.

TDA 9817

As for TDA9818, without the option for processing AM audio

and positive video modulation (SECAM L,L’).

9.5.6

Audio demodulator

Multi-standard audio processor MSP 3415D

The MSP 3415D [7761] is a multi-standard sound processor

which can demodulate FM Mono/Stereo, NICAM and AM

signals. The incoming signal is first controlled and then

digitised. The digital signal is then demodulated in 2 separate

channels. In the first MSP channel, FM and NICAM (B/G/I/D/

K) are demodulated, whereas in the second MSP channel,

FM and AM is demodulated again (NICAM L corresponds to

NICAM B/G). These demodulated signals are selected

digitally in the I/O and switched to the D/A converter on the

outputs. Amplitude and bandwidth of the demodulated audio

signals can be determined in the MSP using the

corresponding commands via the I

2

C bus. This means that

the setting required for the best possible performance can be

made.

FM stereo audio decoder TDA 9873

The TDA 9873 [7760] is a multi-standard A2 audio processor

which can demodulate FM mono/stereo signals. The audio IF

SIF2 is passed from pin 3 [7705] to pin 25 [7760]. The

demodulated stereo signals AFL and AFR I

2

C bus are

available controlled on pins 1 and 2.

9.6

Video signal processing VS (VS part)

9.6.1

Switchover functions in the signal electronics IC

LA71695xM [7004]:

The signal electronics IC LA71595M [7004] are controlled via

the I

2

C Bus on pins 23 and 24 by the AIO.

As groups 5 and 6 can only be transferred with a change in

HP1, it must be ensured that during measurements the HP1

line is always connected to the SE IC or replaced by a

corresponding signal.

REC/PB via IIC bus

During RECORD pin 30 must be passed via [7009] on 5V

(IREV=LOW) to activate the video write current stages. To

keep the transient condition of the write current as short as

possible, the signal electronics IC is set to REC via IIC bus

before the pin 30 change.

PAL/SECAM/MESECAM/NTSC via IIC bus

SP/LP/SLP via IIC bus

VIDEO INPUT SELECTOR SWITCH via IIC bus

In 1-scart units a distinction is made via the IIC bus between

VFV (pin 36 / VID2) and VBS which corresponds to VIN1 (pin

38 / VID1). In 2-scart units the video input selection is made

via IIC bus in the STV6401 [7904] and the SE IC is always on

VBS (pin 38 / VIN1).

VIDEO ENTRY

The feature frame pulse FFP signal on pin 26 is used to enter

the artificial picture pulse for playback features and the test

picture for the unit installation procedure:

LP/SP head pair switchover

The switchover between the long play LP head pair and the

standard play SP head pair is made via the HSC signal (pin

25).

Head switchover

The video head switchover is made using the HP1 signal (pin

11). To keep audio linear interference as low as possible, the

HP1 polarity should be selected to be inverse and the HP1

level should be the same as the CROT signal on pin 10.

Envelope curve comparator

If the ENVC signal (pin 94) is HIGH, the FM envelope curve

on the LP head is greater than that on the SP head, and vice

versa.

9.6.2

Recording

Luminance

The input signal (1-scart: pin 38 = scart , pin 36 = front end;

2-scart: pin 38 = input video selected using STV6401) is

connected in the IC [7004] and is available uncontrolled on

pin 32 as VREC (SECAM; VPS only unit data slicers). It

reaches pin 31 via an electrolytic capacitor [2036]. In the IC

[7004] the video signal first goes through an amplification

control process (time constants determined by C [2035]).

After the AGC the video signal reaches the FBC clamping

stage (feed back clamp), then the video signal is divided onto

3 paths:

•

Loop-through signal path: The video signal is amplified

by 6dB following video entry and is available controlled

on pin 29 as a VSB signal (OSD entry, data slicer -> I/O,

front end,..).

Loop through

< 0.8V

Test picture

= 1.2 ... 3.8V

Artificial picture pulse

> 4.2V

4/x scanner in play back:SP head pair:1.2V <= HSC <= 2.8V

LP head pair:

0V<= HSC <= 0.8V

2/x scanner in play back:always

3.2V <= HSC <= 5V

PB:

SP1 / LP1:

1.2V <= HP1 <= 2.8V

SP2 / LP2:

0V <= HP1 <= 0.8V

Summary of Contents for VR570

Page 12: ...Direction for use GB 12 VR120 3 3 Direction for use RT111 RT116 RT112 RT114 RT123 RT121 RT128 ...

Page 15: ...Direction for use GB 15 VR120 3 SAT VR870L VR870CC VR720 Set width 435 mm ...

Page 56: ...Service modes Repair tips GB 56 VR120 5 Engineer s remarks ...

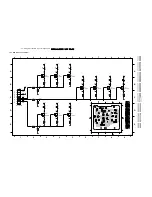

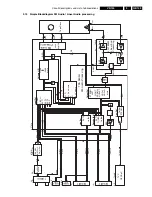

Page 79: ...Circuit diagrams and PWB layouts Wiring diagram 79 VR120 7 7 16 Wiring Diagram Motherboard ...

Page 81: ...Circuit diagrams and PWB layouts Wiring diagram 81 VR120 7 Engineer s remarks ...

Page 82: ...82 VR120 7 Circuit diagrams and PWB layouts Wiring diagram Engineer s remarks ...

Page 83: ...Circuit diagrams and PWB layouts Wiring diagram 83 VR120 7 7 18 Mother board component side ...

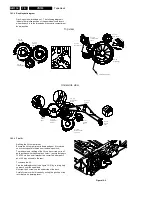

Page 119: ...Tape deck GB 119 VR120 10 ...

Page 123: ...Tape deck GB 123 VR120 10 Engineer s remarks ...