Circuit descriptions and List of abbreviations

GB 106

VR120

9.

9.9

IN/OUT (IO part)

9.9.1

Video

The entire video-I/O is carried out in 2-scart units using the

matrix switch STV6401 [7904), which is controlled by the AIO

via the IIC bus (SDA,SCL). To do this, the following signals

are connected to STV6401 at the inputs: VFV-pin4, VIN1-

pin6, VIN2-pin8, VOUT

1)

-pin10 (

1)

The VOUT signal is also

passed through a voltage divider and a low pass

[2906,3934,3928] and passed to the modulator where

necessary via the emitter follower [7909]) and VFR-pin12

(front cinch input). The outputs OUT3/pin15 (scart 2) and

OUT2/pin16 (scart 1) in the IC are fitted with a 6dB amplifier

and convey the signal to the relevant scart socket. OUT1/

pin2 has no amplifier; this signal (VBS) is passed on to the

VS circuit parts for further processing:

In 1-scart units the SE IC [7004] selects the input video. SE

IC original layout: VIN1 (the VBS line is used in the plan) pin

38 , VFV pin 36. The VOUT1 signal (scart 1 video out) is

generated using an E-follower [7908] from the VOUT signal.

Audio for the 2-scart version:

The output signal for scart 1 is selected using the switch - IC

HEF4053 [7911-C] using the MON control line (pin 9) from

AMLP (pin 5) and AINF_AIN2 (pin 3). The output signal for

scart 2 is selected using the switch - IC HEF4053 [7911-B]

using the DEC control line (pin 10) from AIN1 (pin 2) and AFV

(pin 1).

9.9.2

Decoder mode: (REC or STOP)

Program position with decoder (front end)

The front end signal (VFV or AFV1/2) is passed to the

decoder connected to Scart 2 and from there, goes back to

the VCR via VIN2 or AIN2L/AIN2R .

External input with decoder (9.2.2) is not possible for these

program positions.

External input with decoder

The signal from scart 1-in (normally TV set) is passed to the

decoder connected to scart 2. For scrambled programs, the

decoder switches the pin 8 to high. The VCR then passes the

decoded signal from scart 2-in to scart 1-out.

9.10 Follow Me (FOME part)

This circuit is used to compare the front end video with the

video on scart 1 (video from the TV connected) in order to be

able to save the stations in the same order as on the TV.

The video signals from the front end (VFV) and from the scart

socket (VIN1) are “digitised” using filters and comparators

[7530-C, 7530-D] and compared with one another [7531,

7532, 7530-A]. Low on the output for the circuit means that

the picture contents for the two video signals are identical

and that both receiver parts (TV and VCR) therefore have to

be adjusted for the same station. Possible errors detected

may result with similar signals, e.g. news programmes.

9.11 VPS/PDC, on-screen display (VPO part)

9.11.1 VPS/PDC

The VPS and PDC data is either decoded by the VPS-PDC

decoder-IC SDA5650 [7502] or by the OSD-IC with

integrated VPS, PDC decoder SDA5652 [7502]. Both ICs are

compatible in terms of pins, despite any differences in the

peripherals.

The VPS-PDC data are read from the vertical blanking gap

and stored in the internal RAM. This data is read from the P

via the I

2

C bus.

The time can also be read from the TXT header line (required

for “Time download“). The date is not called up from the TXT

header (various write versions of the preset stations) but only

via PDC format-1.

In the case of the SDA5650 [7502] the input video signal

comes from the signal electronics IC LA71595M [7004-B pin

32] (VREC) via a 470n capacitor [2504] to the data slicer

input on the SDA5650 (pin 17). For the SDA5652 the input

signal from pin 29 (VSB) on the LA71595M [7004-B] comes

via an emitter follower [7501] with a voltage divider to the

data slicer input on the SDA5652 (pin1 17).

9.11.2 OSD-PART

The IC SDA5652 [7502] also allows both the generation of

text keyboard matrices into a video signal and the generation

of an entire picture (full page) for menu-control or if no

background video is available.

The video signal (VSB) passes from the signal electronics IC

LA71595M [7004-B pin 29] via a resistor [3512] to the input

for the OSD-IC [7502 pin 18]. For keyboard matrices in

Secam video signals, a bypass between video-in and video-

out is activated via a switch inside the IC and a band filter

[2507, 5502]. The output signal is available on pin 15.

A multiple of the doubled colour subcarrier oscillation from

the signal electronics (2FSC/8.86MHz) is used as the system

pulse for the IC. It is also used as a reference for generating

the various OSD colours. The signal reaches the IC via a

coupling capacitor [2509].

For the vertical synchronisation of keyboard matrices, an

OSD frame pulse (OFP) is generated by the P [7899-B pin

36] and passed to the IC [7502] on pin 9. The horizontal sync-

pulse is generated using an internal sync-separator and an

internal H-PLL from the video signal on pin 17.

During full-page OSD (menu or no video) neither a vertical-

sync (OFP) nor an H-sync is required, as in this mode, the

OSD-IC generates everything from the system clock

frequency, i.e. all the necessary pulses are generated

internally from the 2FSC signal.

Summary of Contents for VR570

Page 12: ...Direction for use GB 12 VR120 3 3 Direction for use RT111 RT116 RT112 RT114 RT123 RT121 RT128 ...

Page 15: ...Direction for use GB 15 VR120 3 SAT VR870L VR870CC VR720 Set width 435 mm ...

Page 56: ...Service modes Repair tips GB 56 VR120 5 Engineer s remarks ...

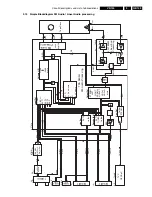

Page 79: ...Circuit diagrams and PWB layouts Wiring diagram 79 VR120 7 7 16 Wiring Diagram Motherboard ...

Page 81: ...Circuit diagrams and PWB layouts Wiring diagram 81 VR120 7 Engineer s remarks ...

Page 82: ...82 VR120 7 Circuit diagrams and PWB layouts Wiring diagram Engineer s remarks ...

Page 83: ...Circuit diagrams and PWB layouts Wiring diagram 83 VR120 7 7 18 Mother board component side ...

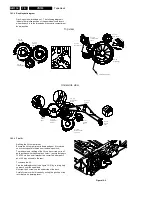

Page 119: ...Tape deck GB 119 VR120 10 ...

Page 123: ...Tape deck GB 123 VR120 10 Engineer s remarks ...