5.4 Trigger and Strobe

5.4.3

Exposure Time Control

The exposure time is defined by the camera. For an active high trigger signal, the camera starts

the exposure with a positive trigger edge and stops it when the programmed exposure time

has elapsed.

External Trigger

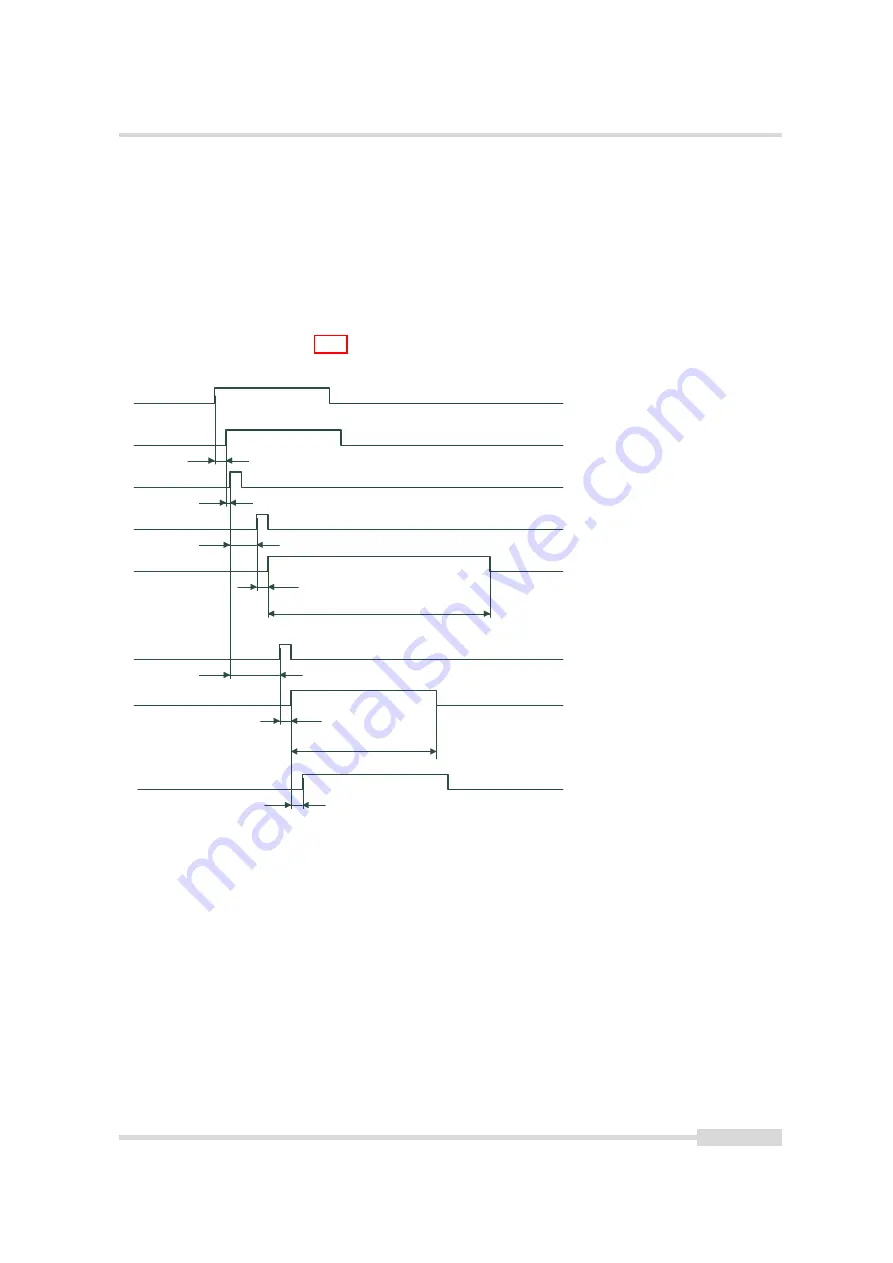

In the external trigger mode with camera controlled exposure time the rising edge of the

trigger pulse starts the camera states machine, which controls the sensor and optional an

external strobe output. Fig. 5.21 shows the detailed timing diagram for the external trigger

mode with camera controlled exposure time.

e

x t e r n a l t r i g g e r p u l s e i n p u t

t r i g g e r a f t e r i s o l a t o r

t r i g g e r p u l s e i n t e r n a l c a m

e r a c o n t r o l

d e l a y e d t r i g g e r f o r s h u t t e r c o n t r o l

i n t e r n a l s h u t t e r c o n t r o l

d e l a y e d t r i g g e r f o r s t r o b e c o n t r o l

i n t e r n a l s t r o b e c o n t r o l

e x t e r n a l s t r o b e p u l s e o u t p u t

t

d - i s o - i n p u t

t

j i t t e r

t

t r i g g e r - d e l a y

t

e x p o s u r e

t

s t r o b e - d e l a y

t

d - i s o - o u t p u t

t

s t r o b e - d u r a t i o n

t

t r i g g e r - o f f s e t

t

s t r o b e - o f f s e t

Figure 5.21: Timing diagram for the camera controlled exposure time

The rising edge of the trigger signal is detected in the camera control electronic which is

implemented in an FPGA. Before the trigger signal reaches the FPGA it is isolated from the

camera environment to allow robust integration of the camera into the vision system. In the

signal isolator the trigger signal is delayed by time t

d

−

iso

−

input

. This signal is clocked into the

FPGA which leads to a jitter of t

jitter

. The pulse can be delayed by the time t

trigger

−

delay

which

can be configured by a user defined value via camera software. The trigger offset delay

t

trigger

−

offset

results then from the synchronous design of the FPGA state machines. The

exposure time t

exposure

is controlled with an internal exposure time controller.

The trigger pulse from the internal camera control starts also the strobe control state machines.

The strobe can be delayed by t

strobe

−

delay

with an internal counter which can be controlled by

the customer via software settings. The strobe offset delay t

strobe

−

delay

results then from the

synchronous design of the FPGA state machines. A second counter determines the strobe

duration t

strobe

−

duration

(strobe-duration). For a robust system design the strobe output is also

MAN075 05/2017 V1.0

57 of 127

Summary of Contents for MV1-D2048-3D06 series

Page 10: ...1 Preface 10 of 127 MAN075 05 2017 V1 0...

Page 12: ...2 Introduction 12 of 127 MAN075 05 2017 V1 0...

Page 26: ...3 How to get started 3D GigE G2 26 of 127 MAN075 05 2017 V1 0...

Page 32: ...4 Product Specification 32 of 127 MAN075 05 2017 V1 0...

Page 66: ...5 Functionality 66 of 127 MAN075 05 2017 V1 0...

Page 82: ...6 Precautions 82 of 127 MAN075 05 2017 V1 0...

Page 120: ...12 Support and Repair 120 of 127 MAN075 05 2017 V1 0...

Page 122: ...13 References 122 of 127 MAN075 05 2017 V1 0...