48

BD-V1100, BD-V1110

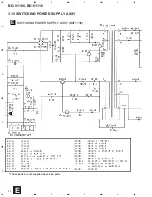

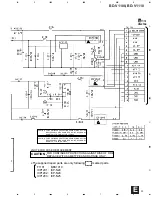

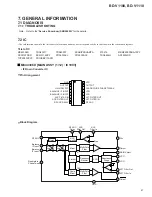

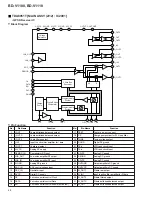

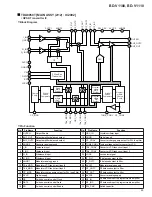

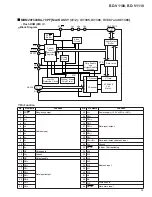

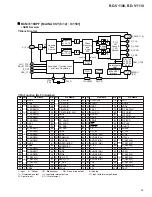

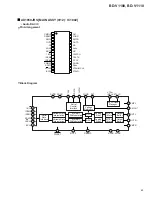

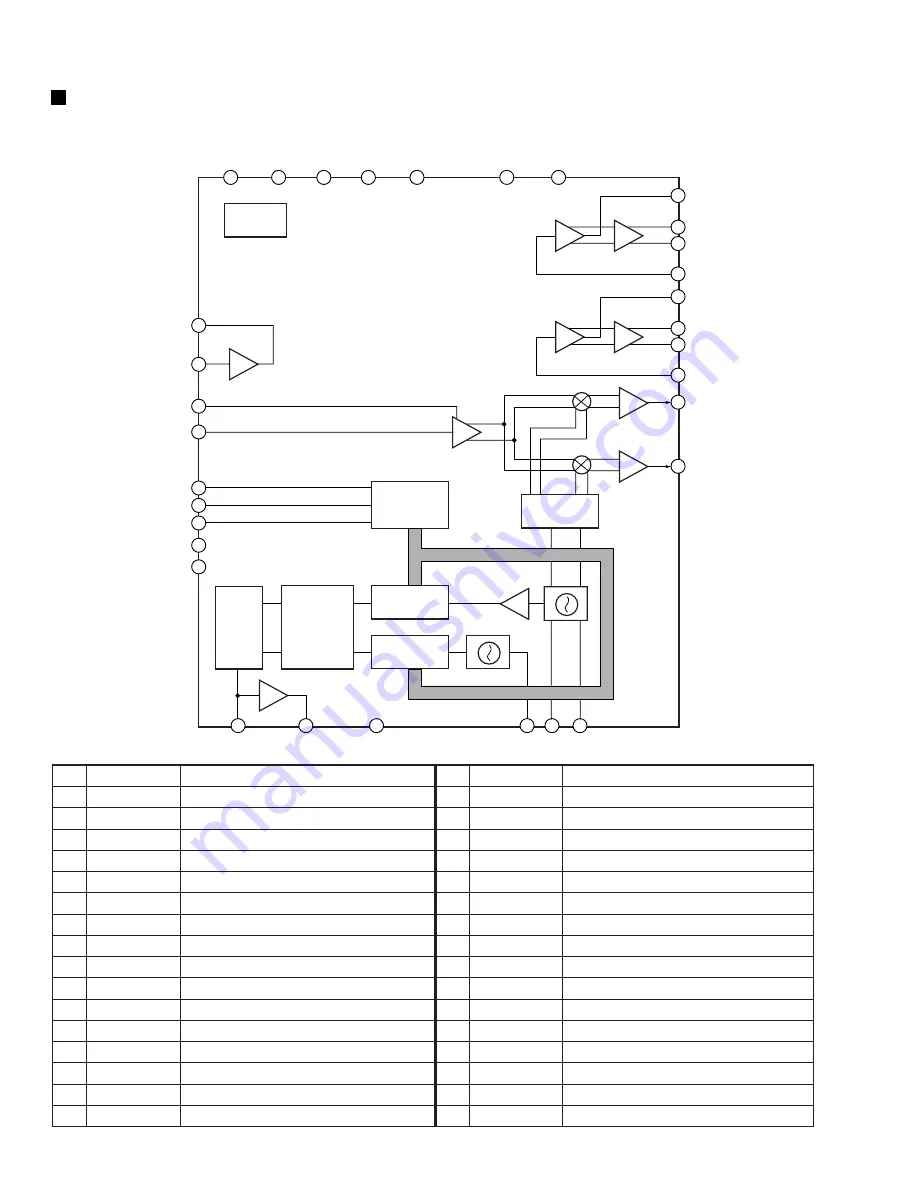

TDA8051T [MAIN ASSY (2/12) : IC2001]

• QPSK Receiver IC

•

Block Diagram

•

Pin Function

Charge

Pump

Digital Phase

Comparator

Programmable

Divider

Programmable

Divider

Voltage

Reference

3 Wire Bus

Tranceiver

90

CK

OSC_IN

12

TEST

17

TKa

22

TKb

21

Q_OUT1

28

I_OUT1

5

I_IN1

4

I_OUTC

2

I_OUT

1

I_OUT2

3

OUTGND

26

OUTVCC

27

A3VCC

25

A1GND

10

A1VCC

6

A2GND

24

A2VCC

23

TUNE

19

CP

18

14

DEMOD_IN 7

AGC_IN 11

LNA_IN 9

LNA_OUT 8

DATA

15

EN

16

DVCC 13

DGND 20

Q_IN1

29

Q_OUTC

31

Q_OUT

32

Q_OUT2

30

0

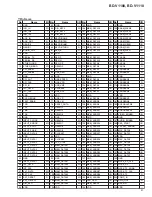

No.

Pin Name

Function

No.

Pin Name

Function

1

I_OUT

I data bufferised balanced output

17

TEST

Test pin : do not connect

2

I_OUTC

I data bufferised balanced output

18

CP

Charge pump output for PLL loop filter

3

I_OUT2

I data filtered output

19

TUNE

Tuning voltage output

4

I_IN1

Input to active filter amplifier for I data

20

DGND

Digital DC ground

5

I_OUT1

I data raw output

21

TKb

VCO tank circuit input

6

A1VCC

Analog DC supply

22

TKa

VCO tank circuit input

7

DEMOD_IN

Demodulator RF input

23

A2VCC

Analog DC supply

8

LNA_OUT

Low noise amplifier RF output

24

A2GND

Analog DC ground

9

LNA_IN

Low noise amplifier RF input

25

A3VCC

Analog DC supply

10

A1GND

Analog DC ground

26

OUTGND

Output amplifiers DC ground

11

AGC_IN

AGC control voltage input

27

OUTVCC

Output amplifiers DC supply

12

OSC_IN

Oscillator input

28

Q_OUT1

Q data raw output

13

DVCC

Digital DC supply

29

Q_IN1

Input to active filter amplifier for Q data

14

CK

3 wire bus serial control Clock

30

Q_OUT2

Q data filtered output

15

DATA

3 wire bus serial control Data

31

Q_OUTC

Q data bufferised balanced output

16

EN

3 wire bus serial control Enable (active low)

32

Q_OUT

Q data bufferised balanced output