60

BD-V1100, BD-V1110

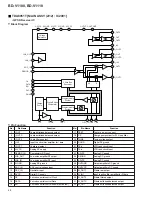

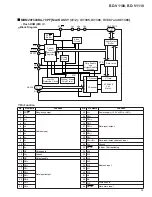

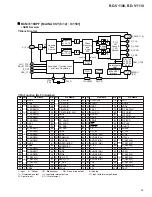

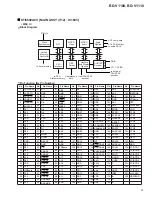

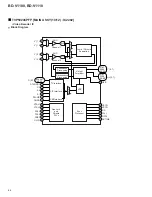

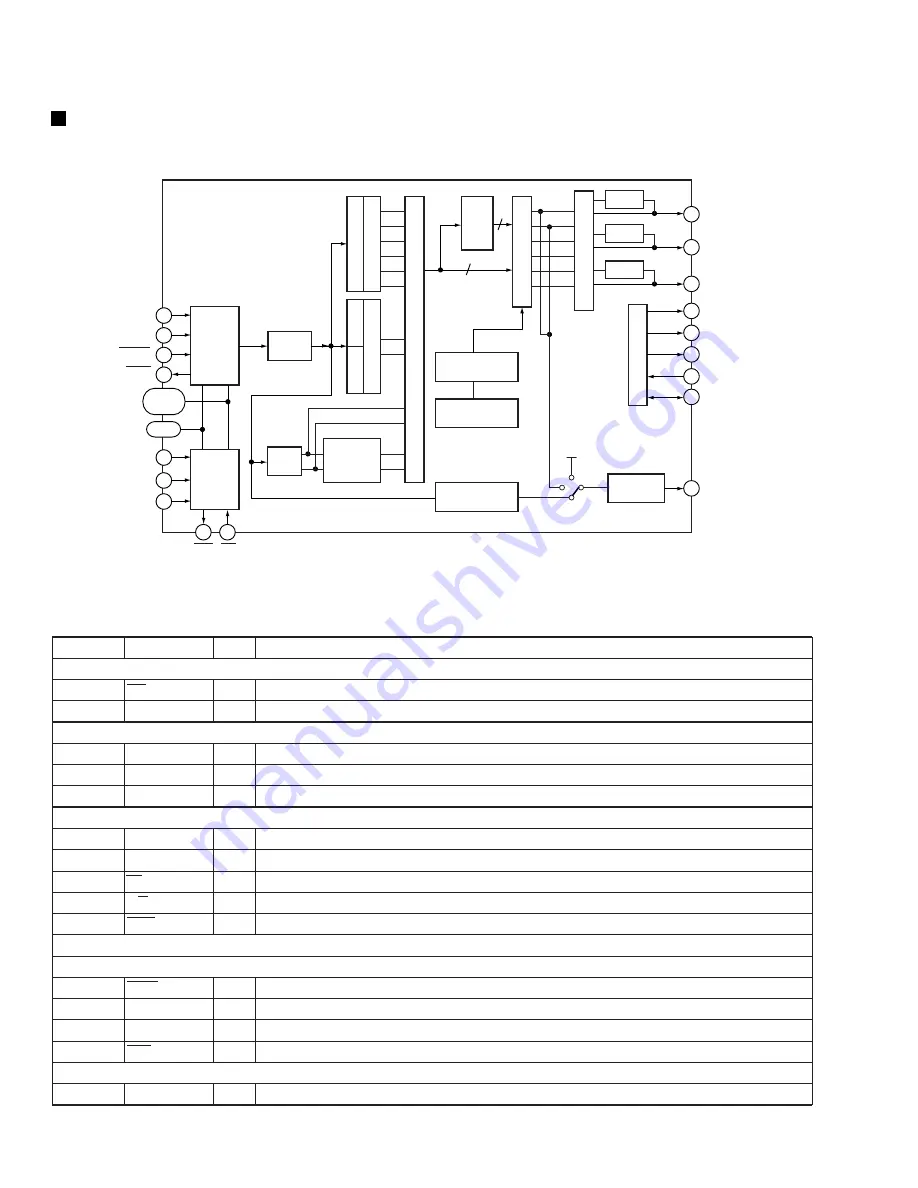

STI4600ACV [MAIN ASSY (8/12) : IC1701]

• AC-3 Decoder IC

•

Block Diagram

4

6

PES

Parser

L

R

C

Lfe

Ls

Rs

Delay

PCM

IRQ CS

Down-

sampling

96/48kHz

Packet

Formatter PTS

IEC958

Formatter

Pink Noise

Generator

Programmable

Switch

L

T

R

T

Buffer

Control

SIN

LRCLKIN

DSTR

REQ

D[0:7]

A[0:7]

PCM_OUT0

41

39

40

MAINI2CADR

42

SCLKI2C

46

SDAI2C

44

57

38

59

73

PCM_OUT1

74

PCM_OUT2

75

80,1-4,

7-9

15-22

MPEG1

MPEG2

DO

WNMIX

A

C-3

DO

WNMIX

Prologic

Decoder

SWITCH

SWITCH

HPF/LPF Subw

oof

er

PLL and Cloc

ks

L

R

C

Lfe

Ls

Rs

L

R

L

R

L

R

Delay

Delay

SCLK

63

LRCLK

64

CLKOUT

26

I958OUT

Encoder

1-2: I958OUT outputs S/PDIF null data

1-3: I958OUT outputs S/PDIFPCM (non-compressed data)

1-4: I958OUT outputs S/PDIF AC-3 or MPEG2 (compressed data)

Mute

1

2

3

4

PCM

61

CLK

36

PCMCLK

67

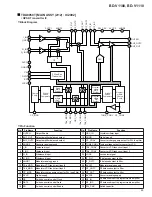

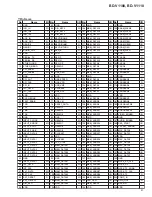

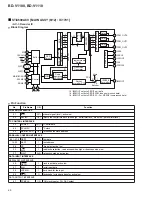

No.

Pin Name

I/O

Function

CONTROL INTERFACES

57

IRQ

O(1) Interrupt signal (level), active low

45

SELI2C

I(2)

Selects the control interface (when high : serial interface, when low : parallel interface)

I

2

C CONTROL INTERFACE

44

SDAI2C

I/O(1) I

2

C serial data

46

SCLKI2C

I

I

2

C clock

42

MAINI2CADR

I(2)

Detemines the slave address

PARALLEL CONTROL INTERFACE

80,1-4,7-9 D0-D7

I/O

Host data

15-22

A0-A7

I

Host address

38

CS

I

Chip select, active low

23

R/W

I

Read/write selection : read access when high, write access when low

37

WAIT

O(3) Data acknowledge, active low

DATA INPUT INTERFACE

SERIAL DATA INTERFACE

40

DSTR

I

Clock input data, active low

41

SIN

I

Serial input data

39

LRCKIN

I

Word clock for the input

59

REQ

O

Handshake for the data transfer, active low

DATA OUTPUT INTERFACE

67

PCMCLK

I/O

PCM clock input or PLL DAC output

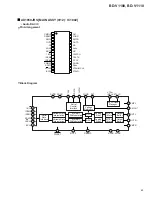

•

Pin Function