67

BD-V1100, BD-V1110

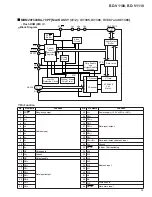

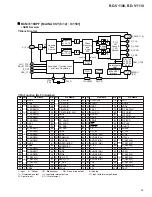

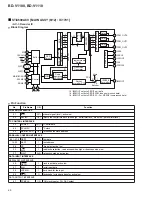

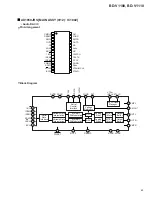

PDIUSBP11APW [MAIN ASSY (12/12) : IC1201]

• USB Driver IC

•

Pin Arrangement

OE#

D –

D +

2

10

11

SPEED 9

V

MO

/F

SEO

13

V

PO

12

RCV 3

V

P

4

V

M

5

MODE

OE#

RCV

V

P

V

M

SUSPND

GND

V

CC

V

MO

/F

SEO

VPO

D +

D –

SPEED

NC

1

2

3

4

5

6

7

14

13

12

11

10

9

8

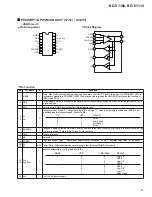

No.

Pin Name

I/O

Function

1

MODE

I

Mode. When left unconnected a weak pull-up transistor pulls it to VCC and in this mode, the PDIUSBP11APW is

backward compatible to PDIUSBP11APW. When connected to ground the VMO/FSEO pin takes the function of

FSEO (force SEO)

2

OE#

I

Output enable. Active low, enables the transceiver to transmit data on the bus. When not active the transceiver is

in receive mode.

3

RCV

O

Receive data. CMOS level output for USB differential input.

4

5

V

P

V

M

O

Gated version of D- and D+. Outputs are logic "0" and logic "1". Used to detect single ended zero (SE0#), error

conditions and interconnect speed. (Inputs to SIE)

VP

VM

RESULT

0

0

1

1

0

1

0

1

SE0#

Low Speed

Full Speed

Error

6

SUSPND

I

Suspend. Enables a low power state while the USB bus is inactive. While the SUSPND pin is active it will drive the

RCV pin to a logic "0" state. Both D+ and D- are tri-stated.

7

GND

−

Ground reference

8

NC

−

Not used

9

SPEED

I

Edge rate control. Logic "1" operates at edge rates for "full speed". Logic "0" operates edge rates for "low speed".

10

11

D+

D-

AI/O Data+, Data-. Differential data bus conforming to the Universal Serial Bus standard.

12

13

V

PO

V

MO

/F

SEO

I

Inputs to differential drive. (Outputs from SIE).

MODE

VPO

VMO/FSEO

RESULT

0

0

0

1

1

0

1

0

1

Logic "0"

SE0#

Logic "1"

SEO#

1

0

0

1

1

0

1

0

1

SE0#

Logic "0"

Logic "1"

Illegal code

14 V

CC

−

3.0V to 3.6V power supply

•

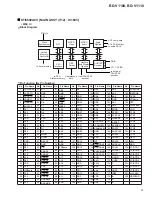

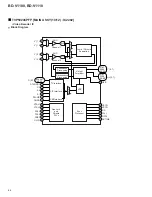

Block Diagram

•

Pin Function