CD-UB100/XN/UC

30

1

2

3

4

1

2

3

4

C

D

F

A

B

E

-

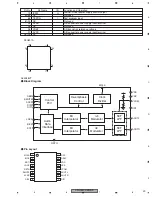

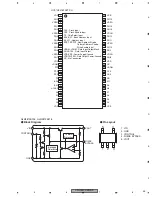

Pin Functions(TCC8600-00X-EA-AG)

Pin No.

Pin Name

I/O

Function and Operation

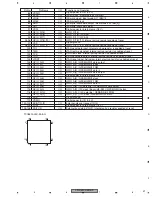

1

2-6

7

8

9

10-16

17-23

24

25

26

27-39

40

41,42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

VSS

XD[4]-[8]

VDDI

VSS

VDDIO

XD[9]-[15]

XA[0]-[6]

VDDI

VSS

VDDIO

XA[7]-[19]

VDDI

XA[20], [21]

VDDIO

SD_CLK

VSS

SD_CKE

SD_nCS

nWE

nOE

nCS[0]/ND_nOE[0]

nCS[1]/ND_nOE[1]

nCS[2]/ND_nOE[2]

nCS[3]/ND_nOE[3]

XOUT

XIN

XTOUT

XTIN

VDDI

VSS

GPIO_B[6]

ND_nWE

UART0TXD

UART0RXD

READY

VDDIO

ADIN4

ADIN2

ADIN0

VDDADC

VSSADC

VSSPLL1

XFILT1

VDDPLL1

VDDPLL

XFILT

VSSPLL

nRESET

MODE1

USBH0_DN

USBH0_DP

VSS

USBH1_DN

USBH1_DP

VDDUSB

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I

O

I

I/O

I/O

I/O

I/O

I

I

I

I/O

I/O

I/O

I/O

Digital ground

External bus data bit [4]-[8]. Internal pull-up resistor enabled at reset.

Digital power for internal core (1.8 V)

Digital ground

Digital power for I/O (3.3 V)

External bus data bit [9]-[15]. Internal pull-up resistor enabled at reset.

External bus address bit [0]-[6]

Digital power for internal core (1.8 V)

Digital ground

Digital power for I/O (3.3 V)

External bus address bit [7]-[19]

Digital power for internal core (1.8 V)

External bus address bit [20], [21]

Digital power for I/O (3.3 V)

SDRAM clock

Digital ground

SDRAM clock enable signal. Active high.

Chip select signal for SDRAM, active low

Static memory write enable signal. Active low.

Static memory output enable signal. Active low.

External bus chip select [0] / NAND flash output enable [0]

External bus chip select [1] / NAND flash output enable [1]

External bus chip select [2] / NAND flash output enable [2]

External bus chip select [3] / NAND flash output enable [3]

12 MHz crystal oscillator output

12 MHz crystal oscillator input. Voltage must not exceed VDDI (1.95 V).

32.768 kHz crystal oscillator output

32.768 kHz crystal oscillator input. Voltage must not exceed VDDI (1.95 V).

Digital power for internal core (1.8 V)

Digital ground

GPIO_B[6]

NAND flash WE. Active low

UART0 TX data

UART0 RX data

Ready information from external device.

Digital power for I/O (3.3 V)

General purpose multi-channel ADC input 4

General purpose multi-channel ADC input 2

General purpose multi-channel ADC input 0

Analog power for ADC (3.3 V)

Analog ground for ADC

Analog ground for PLL

PLL1 filter output. 1 200 pF capacitor is required.

Analog & digital power for PLL1 (1.8 V)

Analog & digital power for PLL (1.8 V)

PLL0 filter output. 350 pF capacitor is required.

Analog ground for PLL

System Reset. Active low.

Mode setting input 1. Pull-down for normal operation.

USB host port 0 D- signal

USB host port 0 D+ signal

Digital ground

USB host port 1 D- signal

USB host port 1 D+ signal

Power for USB I/O (3.3 V)

Summary of Contents for CD-UB100

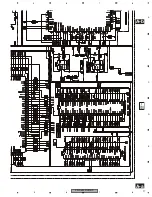

Page 5: ...CD UB100 XN UC 5 5 6 7 8 5 6 7 8 C D F A B E 1 SPECIFICATIONS ...

Page 14: ...CD UB100 XN UC 14 1 2 3 4 1 2 3 4 C D F A B E A a A b A b 1 1 8 mH A MOTHER UNIT ...

Page 17: ...CD UB100 XN UC 17 5 6 7 8 5 6 7 8 C D F A B E A a A b A b A a 220 0R0 R632 47K ...

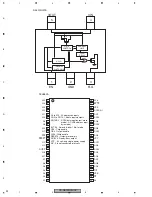

Page 36: ...CD UB100 XN UC 36 1 2 3 4 1 2 3 4 C D F A B E 8 OPERATIONS ...

Page 37: ...www mobiteh com ...