CDJ-800MK2

131

5

6

7

8

5

6

7

8

C

D

F

A

B

E

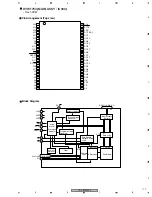

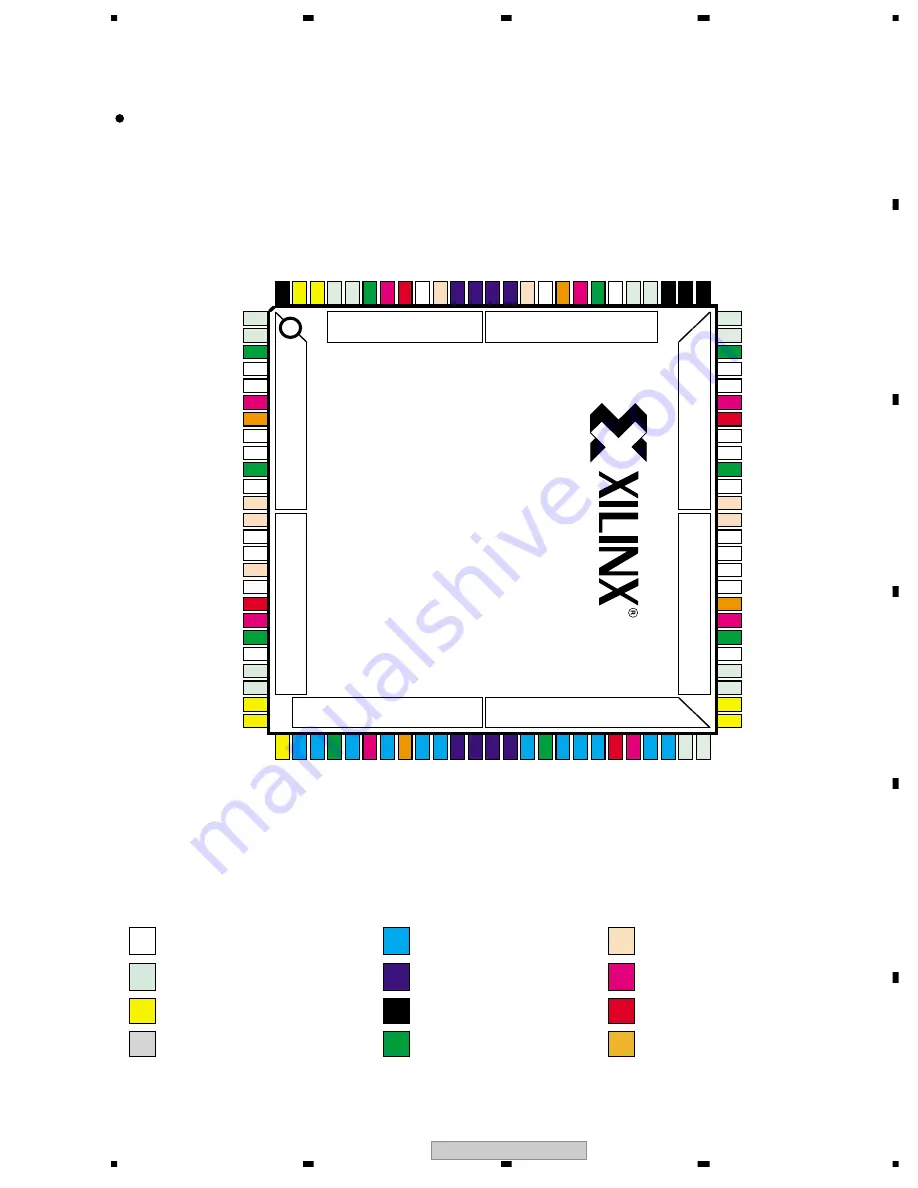

XC3S50-4VQG100C-K (MAIN ASSY : IC302)

• FPGA IC

Figure 5 :

VQ100 Package Footprint (top view). Note pin 1 indicator in top-left corner and logo orientation.

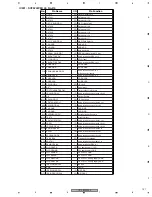

22

I/O:

Unrestricted, general-purpose user I/O

12

DUAL:

Configuration pin, then possibl

user I/O

7

VREF:

User I/O or input voltage reference for

bank

14

DCI:

User I/O or reference resistor input for

bank

8

GCLK:

User I/O or global clock buffer

input

8

VCCO:

Output voltage supply for bank

7

CONFIG:

Dedicated configuration pins

4

JTAG:

Dedicated JTAG port pins

4

VCCINT:

Internal core voltage supply (+1.2V)

0

N.C.:

No unconnected pins in this package

10

GND:

Ground

4

VCCAUX:

Auxiliary voltage supply (+2.5V)

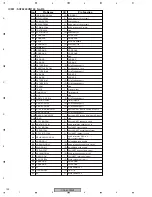

TDI

PROG_B

HSWAP_EN

IO_L01N_0/VRP_0

IO_L01P_0/VRN_0

GND

VCCO_0

VCCINT

IO_L31N_0

IO_L31P_0/VREF_0

IO_L32N_0/GCLK7

IO_L32P_0/GCLK6

IO_L32N_1/GCLK5

IO_L32P_1/GCLK4

IO_L31N_1/VREF_1

IO_L31P_1

VCCAUX

VCCO_1

GND

IO

IO_L01N_1/VRP_1

IO_L01P_1/VRN_1

TMS

TCK

TDO

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

1

75

IO_L01N_2/VRP_2

2

74

IO_L01P_2/VRN_2

3

73

GND

4

72

IO_L21N_2

5

71

IO_L21P_2

VCCO_7

6

70

VCCO_2

VCCAUX

7

69

VCCINT

8

68

IO_L24N_2

9

67

IO_L24P_2

10

66

GND

11

65

IO_L40N_2

12

64

IO_L40P_2/VREF_2

13

63

IO_L40N_3/VREF_3

14

62

IO_L40P_3

IO_L24P_6

IO_L40P_7

IO_L23P_7

IO_L21P_7

IO_L21N_7

IO_L23N_7

IO_L40N_6

15

61

IO_L24N_3

16

60

IO_L24P_3

IO

17

59

IO

VCCINT

18

58

VCCAUX

VCCO_6

19

57

VCCO_3

GND

GND

GND

IO_L01N_6/VRP_6

IO_L01P_6/VRN_6

IO_L24N_6/VREF_6

IO_L40N_7/VREF_7

IO_L01P_7/VRN_7

IO_L01N_7/VRP_7

IO_L40P_6/VREF_6

20

56

GND

IO

21

55

IO

22

54

IO_L01N_3/VRP_3

23

53

IO_L01P_3/VRN_3

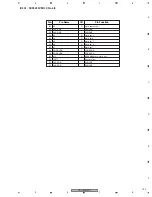

M1

24

52

CCLK

M0

25

51

DONE

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

M2

IO_L01P_5/CS_B

IO_L01N_5/RDWR_B

GND

IO_L28P_5/D7

VCCO_5

IO_L28N_5/D6

VCCAUX

IO_L31P_5/D5

IO_L31N_5/D4

IO_L32P_5/GCLK2

IO_L32N_5/GCLK3

IO_L32P_4/GCLK0

IO_L32N_4/GCLK1

GND

IO_L31N_4/INIT_B

IO_L30P_4/D3

IO_L30N_4/D2

VCCINT

VCCO_4

IO_L27P_4/D1

IO_L27N_4/DIN/D0

IO_L31P_4/DOUT/BUSY

IO_L01P_4/VRN_4

IO_L01N_4/VRP_4

Bank 6

Bank 0

Bank 1

Bank 3

B

ank 2

Bank 4

(no VREF)

Bank 5

(

no VREF, no DCI)

Bank 7

Pin Arrangement (Top view)

Summary of Contents for CDJ-800MK2

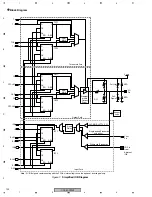

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...