CDJ-800MK2

92

1

2

3

4

1

2

3

4

C

D

F

A

B

E

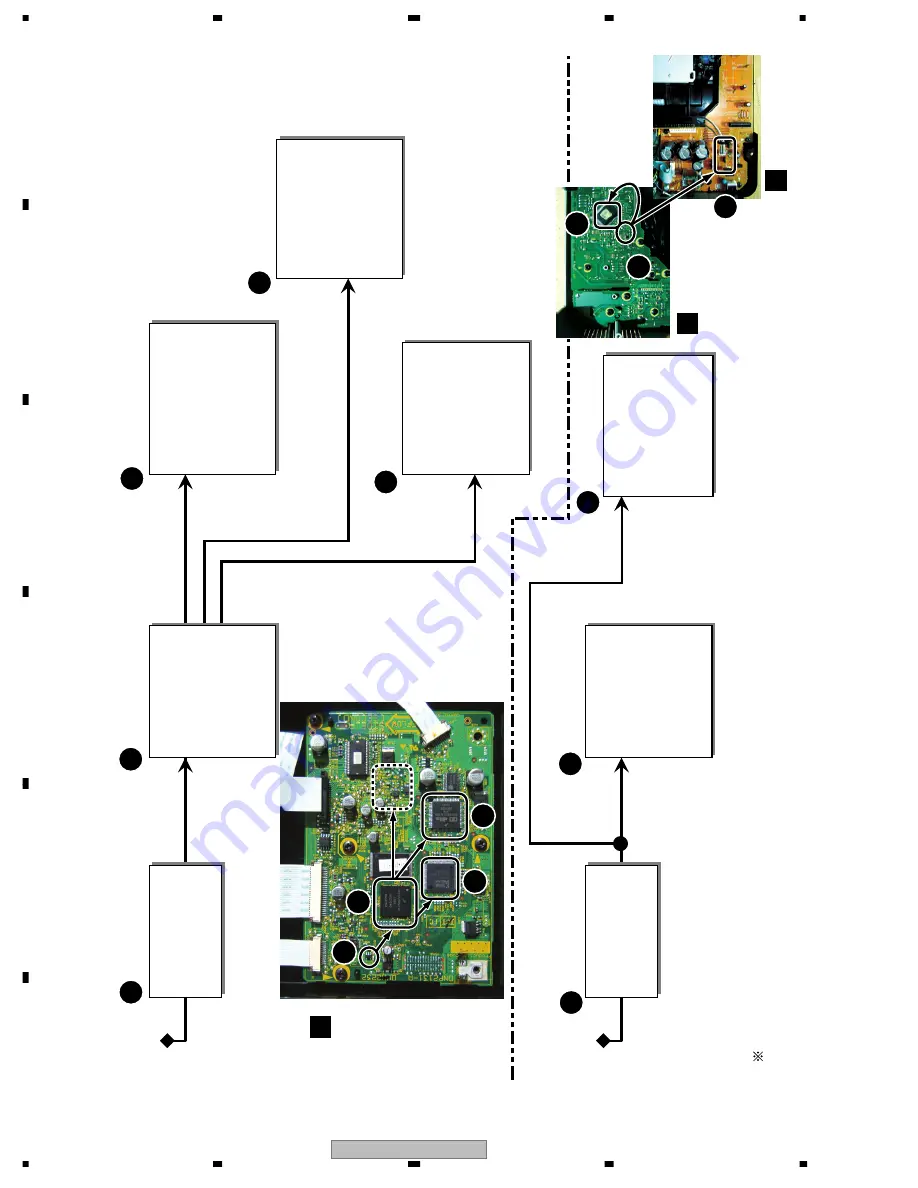

7.1.2 RESET and CLOCK MAP

MAIN ASSY

XRST

PRGM

DC3.3V

DETECT VOLTAGE

3.0V

DELAY TIME

70ms

DSPRST

SRVRST

.DFLB

.DFLB

.SECB

XRST

XRST

DC5V

DETECT VOLTAGE

4.2V

DELAY TIME

70ms

The RESET-LINE name is same as NET-NAME of schematic.

RESET I C

BU4230G

IC304

MPU

SCF5249VM140

AMADEUS

IC301

DSP

DSPC56371AF180

IC701

FPGA

XC3S50-4VQG100C

SPARTAN3

IC302

ServoDSP

TC94A15FG

IC101

RESET I C

BU4242G

IC502

DISPLAY

MPU

M16C/30P Series

PEG237B

IC501

PowerSupply

CIRCUIT

VLD

CDJ-800MK2 RESET ROOT MAP

SECB ASSY

MAIN ASSY

DFLB ASSY

A

A

B

1

1

5

2

2

3

3

4

6

6

B

5

G

C

A

Summary of Contents for CDJ-800MK2

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...