PRO-1010HD

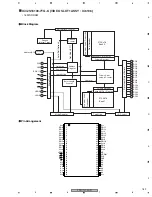

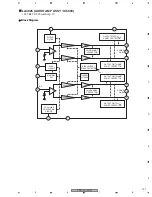

188

1

2

3

4

1

2

3

4

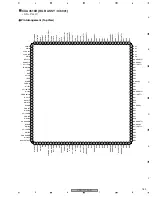

C

D

F

A

B

E

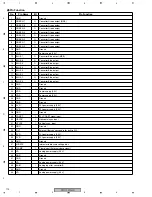

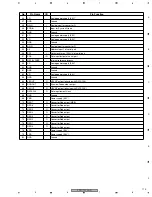

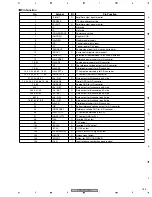

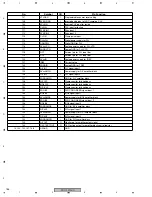

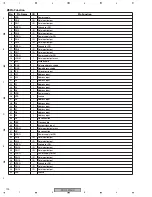

No. Pin Name I/O

Pin Function

No. Pin Name I/O

Pin Function

1

DACVCC

−

DAC power supply (3.3V)

51

Q13

O

24-bit output pixel data bus

2

DACGND

−

DAC ground

52

Q12

O

24-bit output pixel data bus

3

N/C

−

No connection

53

Q11

O

24-bit output pixel data bus

4

N/C

−

No connection

54

Q10

O

24-bit output pixel data bus

5

DACGNDR

−

DAC Red ground

55

Q9

O

24-bit output pixel data bus

6

DACVCCR

−

DAC Red power supply (3.3V)

56

OVCC

−

Output bus power supply (3.3V)

7

AnRPr

O

Red, Pr output of analog video

57

OGND

−

Output bus ground

8

COMP

I

For reference amp. correction of DAC inside

58

Q8

O

24-bit output pixel data bus

9

RSET

I

Full scale adjustment resistor input

59

Q7

O

24-bit output pixel data bus

10

DACGNDG

−

DAC Green ground

60

Q6

O

24-bit output pixel data bus

11

DACVCCG

−

DAC Green power supply (3.3V)

61

Q5

O

24-bit output pixel data bus

12

AnGY

O

Green, Y output of analog video

62

Q4

O

24-bit output pixel data bus

13

DACGNDB

−

DAC Blue ground

63

Q3

O

24-bit output pixel data bus

14

DACVCCB

−

DAC Blue power supply (3.3V)

64

VCC

−

Digital power supply (3.3V)

15

AnBPb

O

Blue, Pb output of analog video

65

GND

−

Digital ground

16

GND

−

Digital ground

66

OGND

−

Output bus ground

17

VCC

−

Digital power supply (3.3V)

67

OVCC

−

Output bus power supply (3.3V)

18

RSVDL

I

Reserved Fixed to low.

68

Q2

O

24-bit output pixel data bus

19

RSVDD

O

Reserved No connection

69

Q1

O

24-bit output pixel data bus

20

RSVDD

O

Reserved No connection

70

Q0

O

24-bit output pixel data bus

21

OVCC

−

Output bus power supply (3.3V)

71

INT

O

Interruption output

22

PGND2

−

Audio PLL ground

72

RESET#

I

Reset Activ low.

23

PVCC2

−

Audio PLL power supply (3.3V)

73

RSVDL

I

Reserved Fixed to low.

24

PLLIN

I/O PLL filter input

74

CSCL

I

Configuration I2C clock

25

PLLOUT

I/O PLL filter output

75

CSDA

I/O Configuration I2C data

26

MCCLKOUT

O

Audio master clock output

76

DSDA

I/O DDC I2C data

27

MCCLKIN

I

Reference audio master clock input

77

DSCL

I

DDC I2C clock

28

OGND

−

Output bus ground

78

OGND

−

Output bus ground

29

SPDIF

O

SPDIF audio output

79

PGND1

−

PLL ground

30

SDO

O

I2S serial data output

80

PVCC1

−

PLL power supply (3.3V)

31

WS

O

I2S word selecting output

81

EXT_RES

I

Input impedance adjustment

32

SCK

O

I2S serial clock output

82

AVCC

−

Analog power supply (3.3V)

33

HSYNC

O

Horizontal sync. control signal output

83

RXC-

I

TMDS data input

34

VSYNC

O

Vertical sync. control signal output

84

RXC+

I

TMDS data input

35

DE

O

Data enable

85

AGND

−

Analog ground

36

Q23

O

24-bit output pixel data bus

86

RX0-

I

TMDS data input

37

Q22

O

24-bit output pixel data bus

87

RX0+

I

TMDS data input

38

Q21

O

24-bit output pixel data bus

88

AGND

−

Analog ground

39

Q20

O

24-bit output pixel data bus

89

AVCC

−

Analog power supply (3.3V)

40

VCC

−

Digital power supply (3.3V)

90

AGND

−

Analog ground

41

GND

−

Digital ground

91

RX1-

I

TMDS data input

42

Q19

O

24-bit output pixel data bus

92

RX1+

I

TMDS data input

43

Q18

O

24-bit output pixel data bus

93

AVCC

−

Analog power supply (3.3V)

44

Q17

O

24-bit output pixel data bus

94

AGND

−

Analog ground

45

OGND

−

Output bus ground

95

AVCC

−

Analog power supply (3.3V)

46

ODCK

O

Data clock output

96

RX2-

I

TMDS data input

47

OVCC

−

Output bus power supply (3.3V)

97

RX2+

I

TMDS data input

48

Q16

O

24-bit output pixel data bus

98

AGND

−

Analog ground

49

Q15

O

24-bit output pixel data bus

99

GND

−

Digital ground

50

Q14

O

24-bit output pixel data bus

100 VCC

−

Digital power supply (3.3V)

Pin Function