26

HTP-071

1

2

3

4

A

B

C

D

E

F

1

2

3

4

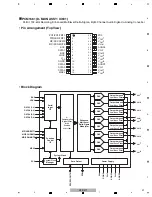

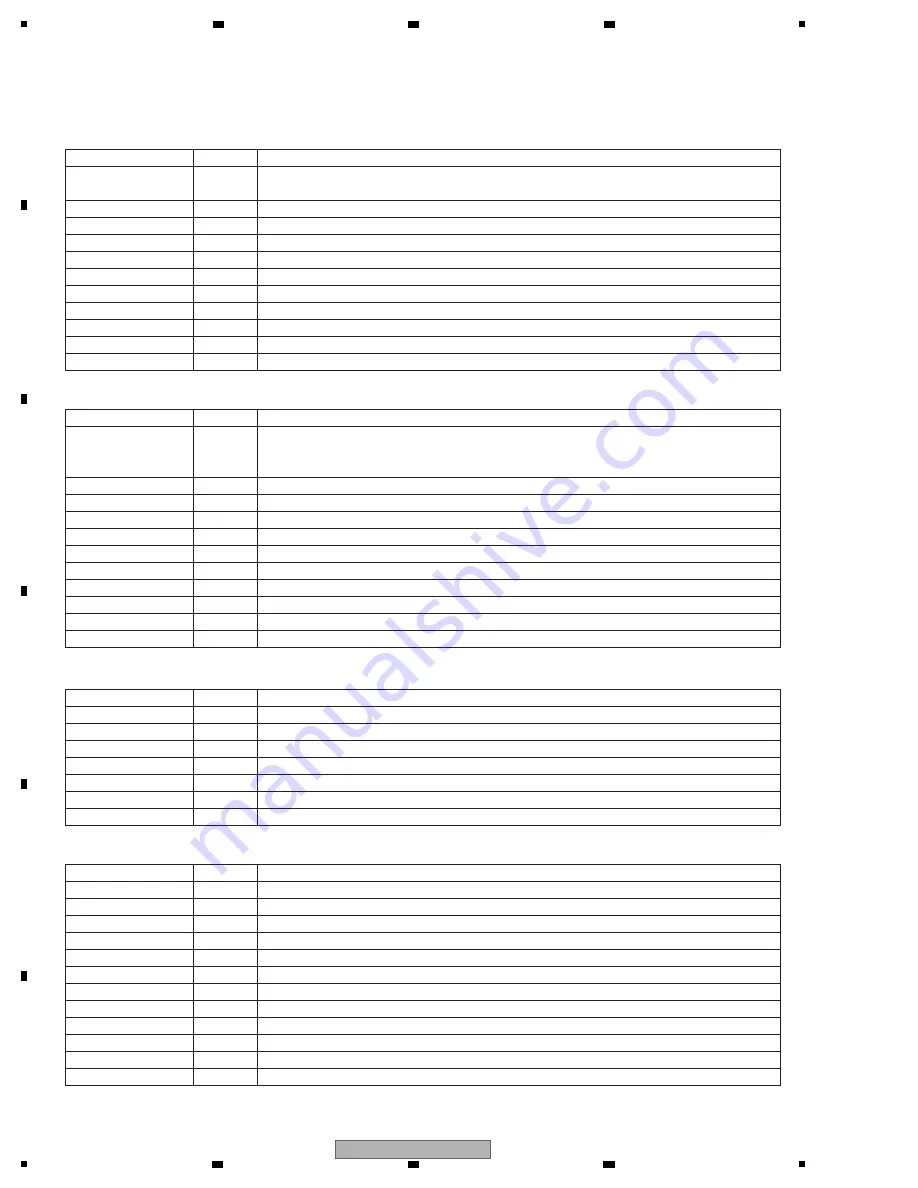

• Pin Function

Name

Audio Outputs

In/Out

Description

MCLK

OUT

System Clock output for audio DAC (128/256/384/512 * FSampling_Clock. Connecting a pull-up

(logic 1) or pull-down (logic 0) resistor at this pin defines bit 4 of the slave IIC Address

IIS_SCK

OUT

IIS SCK output for IIS audio port. Sampling clock output for DSD.

IIS_WS

OUT

IIS WS output for all IIS audio ports. DSD audio output port 0 (Right Channel).

IIS_SD0

OUT

IIS SD output for audio port 0 or HBR audio output. DSD audio output port 0 (Left Channel).

IIS_SD1

OUT

IIS SD output for audio port 1 or HBR audio output. DSD audio output port 1 (Right Channel).

IIS_SD2

OUT

IIS SD output for audio port 2 or HBR audio output. DSD audio output port 1 (Left Channel).

IIS_SD3

OUT

IIS SD output for audio port 3 or HBR audio output. DSD audio output port 2 (Right Channel).

SPDIF

OUT

SPDIF output. DSD audio output port 2 (Left Channel).

DSD3R

OUT

DSD audio output port 3 (Right Channel).

DSD3L

OUT

DSD audio output port 3 (Left Channel).

A_MUTE

OUT

Audio Mute Output

Name

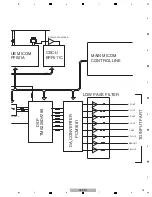

DDC/IIC/MCU/EEPROM

In/Out

Description

I

N

Tb

OUT

Interrupt signal. Asserted when interrupt requests occur. This pin is open drain output when

programmed as active low and external pull-up resistor is needed. This pin is push-pull when

programmed as active high.

MCU_SCL

I

N

SCL signal for slave IIC port

MCU_SDA

IO

SDA signal for slave IIC port

DDC0_SCL

I

N

IIC SCL signal for HDMI Receiver DDC Port 0

DDC0_SDA

IO

IIC SDA signal for HDMI Receiver DDC Port 0

DDC1_SCL

I

N

IIC SCL signal for HDMI Receiver DDC Port 1

DDC1_SDA

IO

IIC SDA signal for HDMI Receiver DDC Port 1

DDC2_SCL

I

N

IIC SCL signal for HDMI Receiver DDC Port 2

DDC2_SDA

IO

IIC SDA signal for HDMI Receiver DDC Port 2

DDC3_SCL

I

N

IIC SCL signal for HDMI Receiver DDC Port 3

DDC3_SDA

IO

IIC SDA signal for HDMI Receiver DDC Port 3

Name

Misc. Pins

In/Out

Description

X_I

N

Analog

External Crystal Input, 18.432 MHz

X_OUT

Analog

External Crystal Output, 18.432 MHz

PLL_XFC_A

Analog

For connecting a capacitor to ground for on-chip PLL

EXT_RSTb

I

N

External Reset input (Active Low) with internal weak pull-up.

PH1

Analog

Connect with 2 k

Ω

pull-up resistor to 3V3.

PH2

Analog

Connect with 2 k

Ω

pull-up resistor to 3V3.

reserved

I

N

Must be tied LOW for normal operation.

Name

Power Pins

In/Out

Description

AVDD

PWR

HDMI Receiver Analog Power (1.8 V)

PVDD

PWR

HDMI Receiver PLL Analog Power (1.8 V)

AVDD33

PWR

HDMI Termination Power (3.3 V)

AVDD18

PWR

HDMI Transmitter Analog Power (1.8 V)

PVDD18

PWR

HDMI Transmitter PLL Analog Power (1.8 V)

AVSS, PVSS

G

N

D

Analog Ground

VDDE

PWR

I/O Power (3.3 V)

VSSE

G

N

D

I/O Ground

VDD

PWR

Internal Logic Power (1.8 V)

VSS

G

N

D

Logic Ground

VDD_PLL

G

N

D

Audio PLL Power (3.3 V)

VSS_PLL

G

N

D

Audio PLL Ground

Summary of Contents for HTP-071

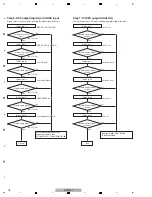

Page 9: ...9 HTP 071 5 6 7 8 5 6 7 8 A B C D E F ...

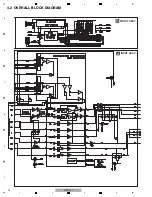

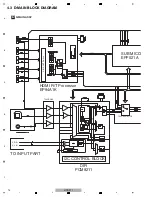

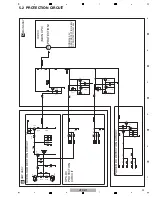

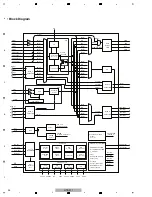

Page 12: ...12 HTP 071 1 2 3 4 A B C D E F 1 2 3 4 4 2 OVERALL BLOCK DIAGRAM H FRONT ASSY A INPUT ASSY ...

Page 89: ...89 HTP 071 5 6 7 8 5 6 7 8 A B C D E F C SIDE B CP1 CP3 CP5 CN1 CN3 ...

Page 93: ...93 HTP 071 5 6 7 8 5 6 7 8 A B C D E F D SIDE B CN600 CP104 ...