2

8

HTP-071

1

2

3

4

A

B

C

D

E

F

1

2

3

4

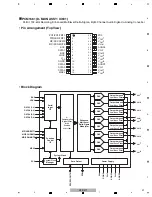

• Pin Function

Name

In/Out

Description

OP_MODE

I

N

Chip operation mode.

0:

N

ormal mode

1: ICP (In Circuit Flash Programming) mode

RSTb

I

N

External Reset (active low) with on-chip pull-up.

When this pin is asserted low, the chip is totally reset.

X_I

N

I

N

24 MHz crystal input

X_OUT

OUT

24 MHz crystal output

P0[7:0]

I

N

/OUT

GPIO port 0 with programmable Open Drain capability.

P1[3:0]

I

N

/OUT

GPIO port 1 or Keyboard Interrupt inputs with internal 20 k

Ω

pull-up to VDD

P2[7:1]

I

N

/OUT

GPIO port 2 with programmable Open Drain capability.

P3[5:0]

OD I

N

/OUT

Open Drain I/O port 3. P3[5:0] shared with IIC.

P4[1:0]

I

N

/OUT

GPIO port 4 or External Interrupt inputs

P5[7:0]

I

N

/OUT

GPIO port 5 with programmable Open Drain capability; 20 mA drive

P6[3:0]

I

N

/OUT

GPIO port 6 with 20 mA drive

P7[4,1:0]

I

N

/OUT

Open Drain I/O port 7. P7[1:0] shared with Serial Port. P7[4] share with CIR.

P8[1:0]

I

N

/OUT

GPIO port 8 with programmable Open Drain capability.

P8[7] and P8[3:0] share with PWM

TIM[1:0]

I

N

/OUT

Timer In/Out or GPIO

SPI_CLK

I

N

/OUT

SPI Clock Out or General Purpose Output

SPI_DO

I

N

/OUT

SPI Data In/Out or General Purpose Output

DP

I

N

/OUT

USB D+ In/Out or GPO

DM

I

N

/OUT

USB D- In/Out or GPO

ADC[1:0]

I

N

/OUT

ADC Inputs or GPIO

VDDA

PWR

Analogue VDD (3.3 V)

VSSA

PWR

Analogue Ground

VDD

PWR

Digital VDD (3.3 V)

VSS

PWR

Digital Ground

Buffer Type

IXDXXP

BDUX8P

XTL24P

XTL24P

BRXX12P

BRUX8P

BRXX8P

BRXX8P

BRXX8P

BRXX24P

BRXX24P

BRXX8P

BRXX8P

BRXX8P

BRXX8P

BRXX8P

USB

USB

ADC

—

—

—

—

Summary of Contents for HTP-071

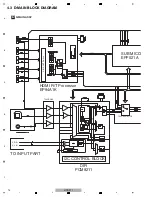

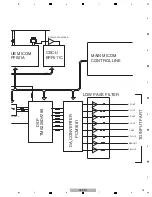

Page 9: ...9 HTP 071 5 6 7 8 5 6 7 8 A B C D E F ...

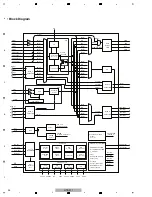

Page 12: ...12 HTP 071 1 2 3 4 A B C D E F 1 2 3 4 4 2 OVERALL BLOCK DIAGRAM H FRONT ASSY A INPUT ASSY ...

Page 89: ...89 HTP 071 5 6 7 8 5 6 7 8 A B C D E F C SIDE B CP1 CP3 CP5 CN1 CN3 ...

Page 93: ...93 HTP 071 5 6 7 8 5 6 7 8 A B C D E F D SIDE B CN600 CP104 ...