30

HTP-071

1

2

3

4

A

B

C

D

E

F

1

2

3

4

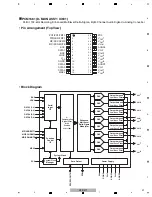

• Pin Function

Name

In/Out

Description

OP_MODE

I

N

Chip operation mode.

0:

N

ormal mode

1: ICP (In Circuit Flash Programming) mode

N

OTE: The input crystal rate will be 24 MHz if this ICP mode is used.

RSTb

I

N

External Reset (active low) with on-chip pull-up.

When this pin is asserted low, the chip is totally reset.

X_I

N

I

N

Crystal input

X_OUT

OUT

Crystal output

P0[2:0]

I

N

/OUT

GPIO port 0 with programmable Open Drain capability.

P11

I

N

/OUT

GPIO port 1 or Keyboard Interrupt inputs with internal 20 k

Ω

pull-up to VDD

P21

I

N

/OUT

GPIO port 2 with programmable Open Drain capability.

P3[5:4, 1:0]

OD I

N

/OUT

Open Drain I/O port 3. Shared with IIC.

P41

I

N

/OUT

GPIO port 4 or External Interrupt inputs

P50

I

N

/OUT

GPIO port 5 with programmable Open Drain capability. 20 mA drive

P7[4,1:0]

I

N

/OUT

Open Drain I/O port 7. P7[1:0] shared with Serial Port. P7[4] share with CIR.

P87

I

N

/OUT

GPIO port 8 with programmable Open Drain capability. Share with PWM

P90

I

N

/OUT

GPIO port 9 with programmable Open Drain capability.

VDD

PWR

Digital VDD (3.3 V)

VSS

PWR

Digital Ground

Buffer Type

IXDXXP

BDUX8P

XTL24P

XTL24P

BRXX12P

BRUX8P

BRXX8P

BRXX8P

BRXX8P

BRXX24P

BRXX8P

BRXX8P

BRXX8P

—

—

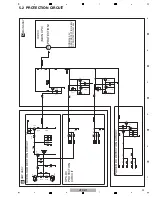

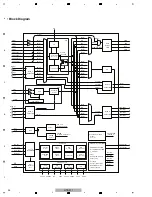

Summary of Contents for HTP-071

Page 9: ...9 HTP 071 5 6 7 8 5 6 7 8 A B C D E F ...

Page 12: ...12 HTP 071 1 2 3 4 A B C D E F 1 2 3 4 4 2 OVERALL BLOCK DIAGRAM H FRONT ASSY A INPUT ASSY ...

Page 89: ...89 HTP 071 5 6 7 8 5 6 7 8 A B C D E F C SIDE B CP1 CP3 CP5 CN1 CN3 ...

Page 93: ...93 HTP 071 5 6 7 8 5 6 7 8 A B C D E F D SIDE B CN600 CP104 ...