32

HTP-071

1

2

3

4

A

B

C

D

E

F

1

2

3

4

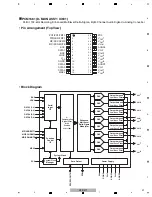

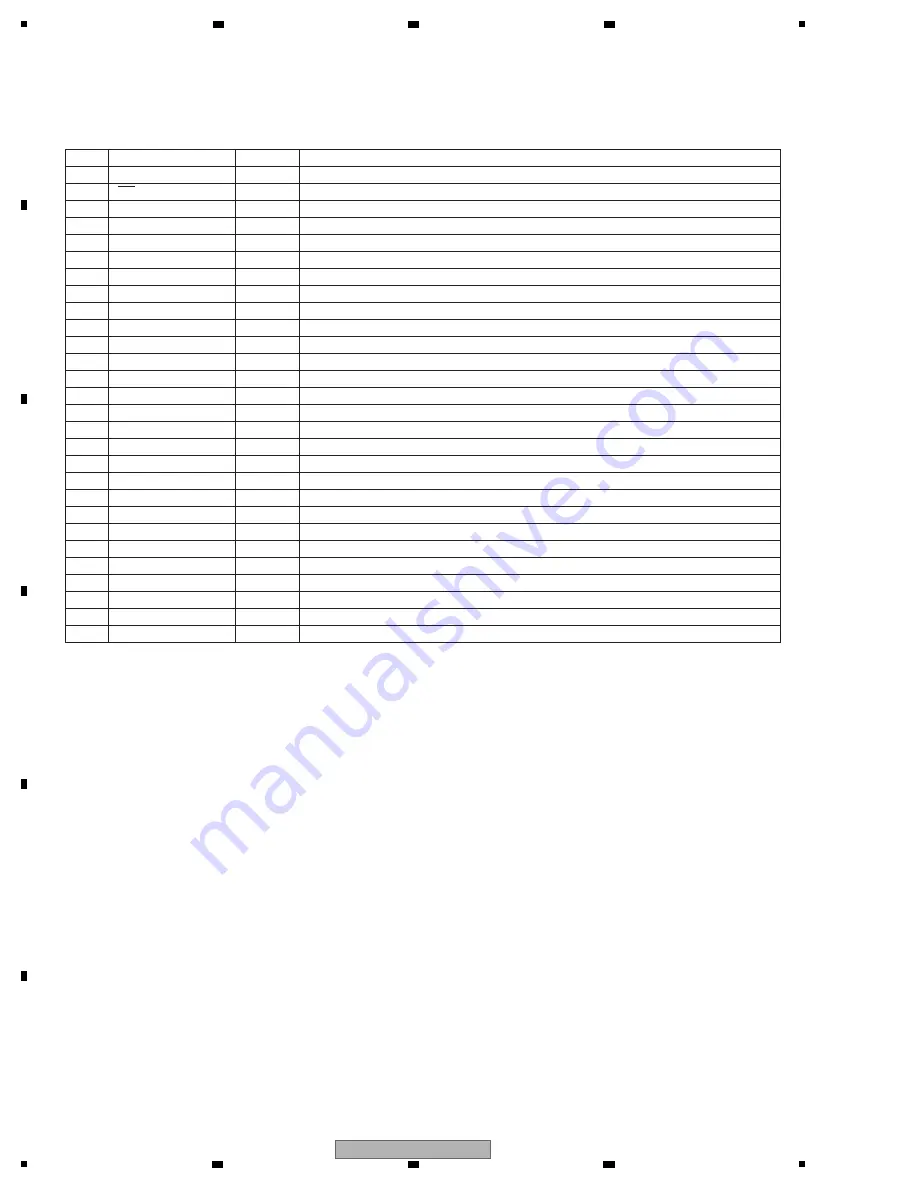

• Pin Function

Name

In/Out

Description

ZR1/ZR1/FMT0

I/O

Zero-flag output 1 for SPI, zero-flag output 1 for I2C, format control input 0 for H/W(1)

MS/ADR/FMT1

I

Select input for SPI, address input for I2C, format control input 1 for H/W (1) (2)

MC/SCL/DEMP

I

Shift clock input for SPI, serial clock input for I2C, de-emphasis control for H/W (1) (2)

MD/SDA/MUTE

I/O

Serial data input for SPI, serial data input/output for I2C, mute control for H/W (1) (2) (3)

SCK

I

System clock input. Input frequency is 128, 192, 256, 384, 512, 768, or 1152 fS. (1) (2)

DATA1

I

Serial audio data input for V

OUT1

and V

OUT2

(1) (2)

BCK

I

Shift clock input for serial audio data (1) (2)

LRCK

I

Left and right clock input. The frequency of this clock is equal to the sampling rate, fS. (1) (2)

V

DD

—

Digital power supply, 3.3-V

DG

N

D

—

Digital ground

DATA3

I

Serial audio data input for V

OUT5

and V

OUT6

(1) (2)

DATA4

I

Serial audio data input for V

OUT7

and V

OUT8

(1) (2)

MSEL

I

Mode control select, I2C, H/W with narrow mode O/S, H/W with wide mode O/S, SPI select(1) (4)

V

OUT8

O

Voltage output for audio signal corresponding to R-ch on DATA4

V

OUT7

O

Voltage output for audio signal corresponding to L-ch on DATA4

V

CC1

—

Analog power supply, 5-V

AG

N

D1

—

Analog ground

V

OUT6

O

Voltage output for audio signal corresponding to R-ch on DATA3

V

OUT5

O

Voltage output for audio signal corresponding to L-ch on DATA3

V

OUT4

O

Voltage output for audio signal corresponding to R-ch on DATA2

V

OUT3

O

Voltage output for audio signal corresponding to L-ch on DATA2

V

CC2

—

Analog power supply, 5-

AG

N

D2

—

Analog ground

V

COM

—

Common voltage output. This pin should be bypassed with a 10-mF capacitor to AG

N

D.

V

OUT2

O

Voltage output for audio signal corresponding to R-ch on DATA1

V

OUT1

O

Voltage output for audio signal corresponding to L-ch on DATA1

ZR2

O

Zero-flag output 2

No.

1

2

3

4

5

6

7

8

9

10

DATA2

I

Serial audio data input for V

OUT3

and V

OUT4

(1) (2)

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

(1) Schmitt-trigger input.

(2) 5-V tolerant.

(3) Open-drain output in I2C mode.

(4) V

DD

/2 biased, quad state input.

Summary of Contents for HTP-071

Page 9: ...9 HTP 071 5 6 7 8 5 6 7 8 A B C D E F ...

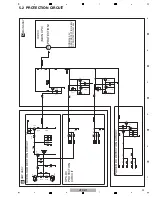

Page 12: ...12 HTP 071 1 2 3 4 A B C D E F 1 2 3 4 4 2 OVERALL BLOCK DIAGRAM H FRONT ASSY A INPUT ASSY ...

Page 89: ...89 HTP 071 5 6 7 8 5 6 7 8 A B C D E F C SIDE B CP1 CP3 CP5 CN1 CN3 ...

Page 93: ...93 HTP 071 5 6 7 8 5 6 7 8 A B C D E F D SIDE B CN600 CP104 ...