35

HTP-071

5

6

7

8

5

6

7

8

A

B

C

D

E

F

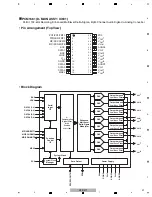

• Pin Function

Name

In/Out

Description

ERROR/I

N

T0

O

DIR Error detection output / Interrupt0 output

N

PCM/I

N

T1

O

DIR

N

on-PCM detection output / Interrupt1 output

MPIO_A0

I/O

Multipurpose I/O, Group A(1)

MPIO_A1

I/O

Multipurpose I/O, Group A(1)

MPIO_A2

I/O

Multipurpose I/O, Group A(1)

MPIO_A3

I/O

Multipurpose I/O, Group A(1)

MPIO_C0

I/O

Multipurpose I/O, Group C(1)

MPIO_C1

I/O

Multipurpose I/O, Group C(1)

MPIO_C2

I/O

Multipurpose I/O, Group C(1)

MPIO_C3

I/O

Multipurpose I/O, Group C(1)

MPIO_B1

I/O

Multipurpose I/O, Group B(1)

MPIO_B2

I/O

Multipurpose I/O, Group B(1)

MPIO_B3

I/O

Multipurpose I/O, Group B(1)

MPO0

O

Multipurpose output 0

MPO1

O

Multipurpose output 1

DOUT

O

Main output port, serial digital audio data output

LRCK

O

Main output port, LR clock output

BCK

O

Main output port, Bit clock output

SCKO

O

Main output port, System clock output

DG

N

D

—

Ground, for digital

DVDD

—

Power supply, 3.3 V (typ.), for digital

MDO/ADR0

I/O

Software control I/F, SPI data output / I2C slave address setting0(2)

MDI/SDA

I/O

Software control I/F, SPI data input / I2C data input/output(2) (3)

No.

1

2

3

4

5

6

7

8

9

10

MPIO_B0

I/O

Multipurpose I/O, Group B(1)

11

12

13

14

15

16

17

18

19

20

21

22

23

24

MC/SCL

I

Software control I/F, SPI clock input / I2C clock input(2)

MS/ADR1

I

Software control I/F, SPI chip select / I2C slave address setting1(2)

MODE

I

Control mode setting, (see the Serial Control Mode section, Control Mode Pin Setting)

RXI

N

7/ADI

N

0

I

Biphase signal, input 7 / AUXI

N

0, serial audio data input(2)

RXI

N

6/ALRCKI0

I

Biphase signal, input 6 / AUXI

N

0, LR clock input(2)

RXI

N

5/ABCKI0

I

Biphase signal, input 5 / AUXI

N

0, bit clock input(2)

RXI

N

4/ASCKI0

I

Biphase signal, input 4 / AUXI

N

0, system clock input(2)

RXI

N

3

I

Biphase signal, input 3(2)

RXI

N

2

I

Biphase signal, input 2(2)

RST

I

Reset Input, active low(2) (4)

VDDRX

—

Power supply, 3.3 V (typ.), for RXI

N

0 and RXI

N

1.

RXI

N

0

I

Biphase signal, input 0, built-in coaxial amplifier

G

N

DRX

—

Ground, for RXI

N

XTI

I

Oscillation circuit input for crystal resonator or external XTI clock source input(5)

XTO

O

Oscillation circuit output for crystal resonator

AG

N

D

—

Ground, for PLL analog

VCC

—

Power supply, 3.3 V (typ.), for PLL analog

FILT

O

External PLL loop filter connection terminal; must connect recommended filter

VCOM

O

ADC common voltage output; must connect external decoupling capacitor

AG

N

DAD

—

Ground, for ADC analog

VCCAD

—

Power supply, 5.0 V (typ.), for ADC analog

VI

N

L

I

ADC analog voltage input, left channel

VI

N

R

(1) Schmitt trigger input

(2) Schmitt trigger input

(3) Open-drain configuration in I2C mode

(4) Onboard pull-down resistor (50 k

Ω

, typical)

(5) CMOS Schmitt trigger input

I

ADC analog voltage input, right channel

25

26

27

28

29

30

31

32

33

34

RXI

N

1

I

Biphase signal, input 1, built-in coaxial amplifier

35

36

37

38

39

40

41

42

43

44

45

46

47

48

Summary of Contents for HTP-071

Page 9: ...9 HTP 071 5 6 7 8 5 6 7 8 A B C D E F ...

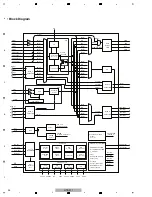

Page 12: ...12 HTP 071 1 2 3 4 A B C D E F 1 2 3 4 4 2 OVERALL BLOCK DIAGRAM H FRONT ASSY A INPUT ASSY ...

Page 89: ...89 HTP 071 5 6 7 8 5 6 7 8 A B C D E F C SIDE B CP1 CP3 CP5 CN1 CN3 ...

Page 93: ...93 HTP 071 5 6 7 8 5 6 7 8 A B C D E F D SIDE B CN600 CP104 ...