MJ-D707, MJ-17D

51

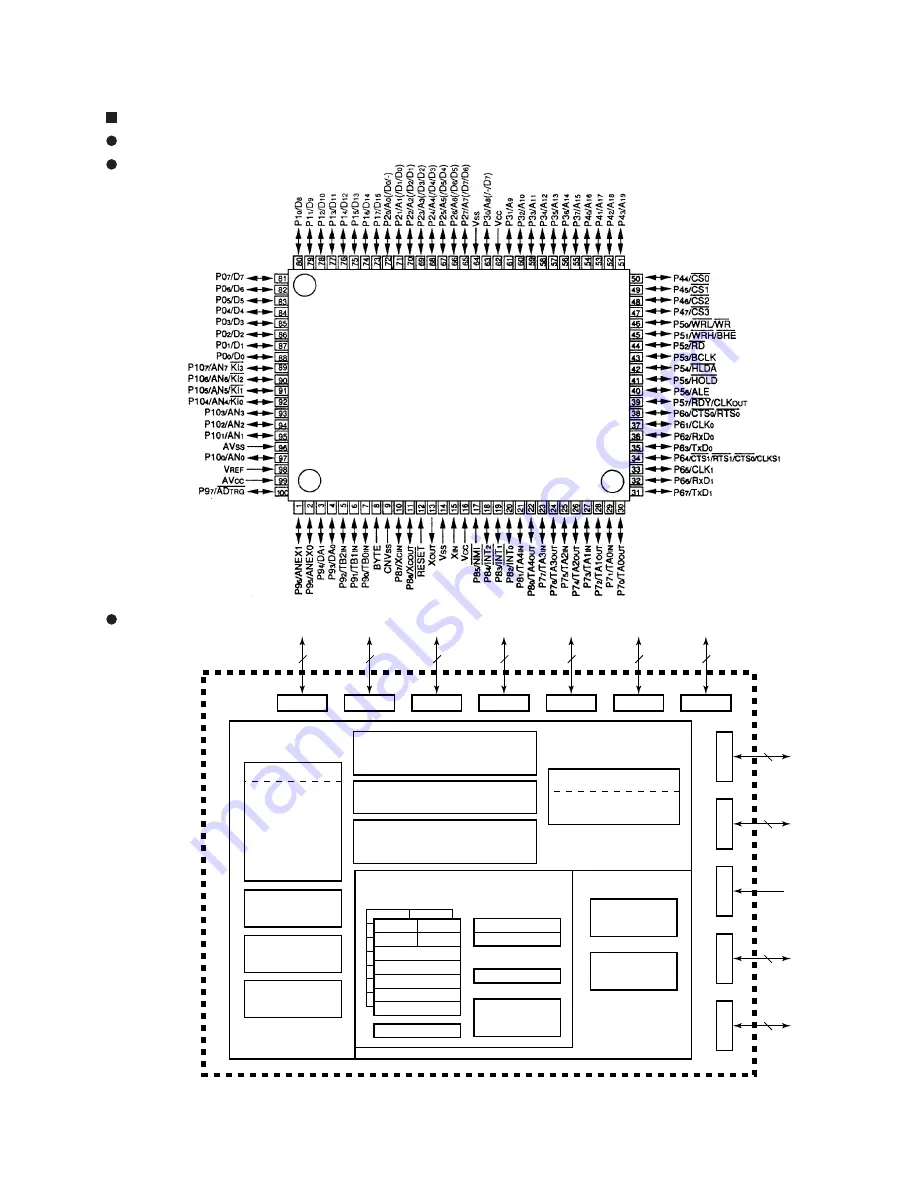

PD5450A (IC104: CORE MAIN UNIT ASSY)

Mechanism Control m-com.

R0H

R0L

R1H

R1L

R2

R3

A0

A1

FB

TIMER

Timer TA0 (16bits)

Timer TA1 (16bits)

Timer TA2 (16bits)

Timer TA3 (16bits)

Timer TA4 (16bits)

Timer TB0 (16bits)

Timer TB1 (16bits)

Timer TB2 (16bits)

DMAC (2 channels)

D/A Converter

(8bits

×

2 channels)

A/D Converter

(10bits

×

8 channels)

(expansion to 10 channels possible)

System clock generation

XIN – XOUT

XCIN – XCOUT

UART/clock-synchronized SI/O

(8bits

×

2 channels)

SB

R0H

R0L

R1H

R1L

R2

R3

A0

A1

FB

INTB

ISP

USP

ROM

MEMORY

16 bits CPU CORE

I/O PORT

RAM

10k bite

Port P0

8

Port P1

8

Port P2

8

Port P3

8

Port P4

8

Port P5

8

Port P6

8

Port P7

8

Port P8

7

Port P85

Port P9

8

Port P10

8

Internal Peripheral

Functions

Monitoring timer

(16 bits)

Register

Stack Pointer

Vector Table

Analog Multiplier

CHC operation circuit

(CCITT method)

(formation polynomial: X

16

+ X

12

+ X

5

+ 1)

Pin Assignment (Top view)

Block Diagram