PDP-5010FD

34

1

2

3

4

1

2

3

4

C

D

F

A

B

E

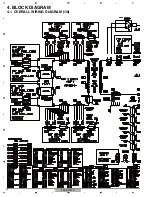

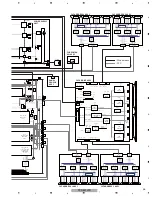

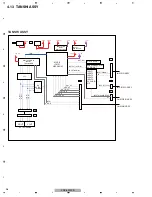

4.11 MAIN ASSY (DTV BLOCK DIAGRAM)

CIMaX sp2

[IC7302]

1Chip System IC

BCM7038KPB1G-B2-K

[IC6401]

SDRAM

[IC6602]

256Mbit

SPDIF out

Tuner

[U6101]

AIR1_V

I2C1

QPSK IF

TS

Demodulate IC

BCM3517

KQLGB0-K

[IC6301]

SAW

filter

RF

AGC

To TANSHI ASSY

[CN4001]

SDRAM

[IC6603]

256 Mbit

SDRAM

[IC6604]

256Mbit

SDRAM

[IC6605]

256 Mbit

QPSK IF

Down Conv.

[IC6201]

IF SW

[IC6103]

EEPROM

64Kbit

IF

.

.

.

HSX_0

I2C_TUNER_SCL

I2C_TUNER_SDA

Logic

Circuit

DVO

[12bit]

OOB_Data

TS0

I2C0

EBI BUS

ME

MO

RY

BUS

UARTA

From EMMA2

To ARIA

To AV_SW

I2C SW

[IC6102]

SCL_AV5

SDA_AV5

From VDEC

YUV(656)

[8bit]

To POD ASSY

[CN4005/CN4006]

FLASH

32M

[IC6902 ]

VBI

SLICER

[IC7001 ]

I2S out

G-Link

IF AGC

From AV_SW

VBI_Y

Summary of Contents for PDP-5010FD

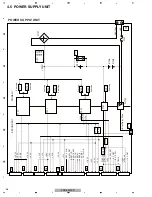

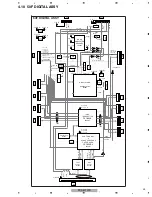

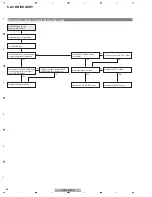

Page 19: ...PDP 5010FD 19 5 6 7 8 5 6 7 8 C D F A B E ...

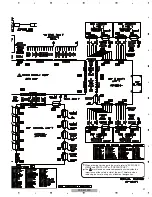

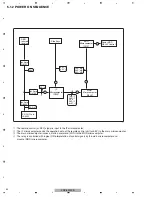

Page 20: ...PDP 5010FD 20 1 2 3 4 1 2 3 4 C D F A B E 4 BLOCK DIAGRAM 4 1 OVERALL WIRING DIAGRAM 1 2 ...

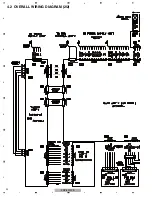

Page 23: ...PDP 5010FD 23 5 6 7 8 5 6 7 8 C D F A B E ...

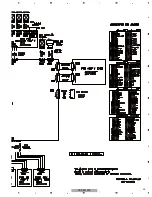

Page 35: ...PDP 5010FD 35 5 6 7 8 5 6 7 8 C D F A B E ...

Page 167: ...PDP 5010FD 167 5 6 7 8 5 6 7 8 C D F A B E ...

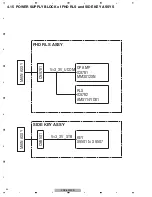

Page 178: ...PDP 5010FD 178 1 2 3 4 1 2 3 4 C D F A B E 10 6 PANEL CHASSIS SECTION ...