PDP-501MX, PDP-V501X

73

FREQUENCY

REFERENCE

XTAL2

XTAL1

OSCILLATOR

AND

TIMING

CPU

PROGRAM

MEMORY

(16K x 8

EPROM)

DATA

MEMORY

(256 x 8 RAM)

TWO 16-BIT

TIMER/EVENT

COUNTERS

COUNTERS

T0

T1

INTERNAL

INTERRUPTS

64K BYTE BUS

EXPANSION

CONTROL

PROGRAMMABLE I/O

PROG SERIAL PORT

FULL DUPLEX UART

SYNCHRONOUS SHIFT

I

2

C SERIAL I/O

SDA

SCL

SHARED

WITH

PORT 1

INT0 INT1

EXTERNAL

INTERRUPTS

CONTROL

PARALLEL PORTS,

ADDRESS/DATA BUS

AND I/O PINS

SERIAL IN

SERIAL OUT

SHARED WITH

PORT 3

LCC

6

7

17

39

29

1

40

28

18

Pin

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

Function

N.C.

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6/SCL

P1.7/SDA

RST

P3.0/R

X

D

NC8

P3.1/T

X

D

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

P3.6/WR

P3.7/RD

XTAL2

XTAL1

V

SS

Pin

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Function

NC8

P2.0/A8

P2.1/A9

P2.2/A10

P2.3/A11

P2.4/A12

P2.5/A13

P2.6/A14

P2.7/A15

PSEN

ALE/PROG

NC8

EA/V

PP

P0.7/AD7

P0.6/AD6

P0.5/AD5

P0.4/AD4

P0.3/AD3

P0.2/AD2

P0.1/AD1

P0.0/AD0

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

ALE

WRD

P0

P1

P2

P3

P4

P5

P6

P7

STROBE

LLA

(12,13.5,16,18MHz)

TEST

SDP

SSC

VACQ

(50/60Hz)

LLDFL

(27,32,36MHz)

LLD

(32,36MHz)

DEFLECTION

TIMING

LOGIC

V

SS

1 to V

SS

4

V

DD

1 to V

DD

4

SRC

HRD

BLND

RE2

RE1

HVCD

WE2

VDFL

HDFL

HRDFL

RSTW1

WE1

CLV

HRA/BLNA

SWC05

SWC1

IE2

IE1

MICROCONTROLLER INTERFACE

SAA4952WP

IE

PROCESSING

+2

ACQUISITION

HORIZONTAL

TIMING

ACQUISITION

VERTICAL

TIMING

HWE1

VACQS

LOGIC

LOGIC

VWE1

DISPLAY

VERTICAL

TIMING

DISPLAY

HORIZONTAL

TIMING

VWE2

VRE1

VRE2

VD

HWE2

HRE

HD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

SAA4952WP

IE1

WE1

STROBE

HRA/BLNA

LLA

IE2

CLV

WE2

HVCD

VACQ

HRDFL

VDFL

LLDFL

HDFL

P7

P6

P5

P4

SWC05

SDP

SRC

SWC1

HRD

V

DD1

V

SS4

V

SS2

V

DD3

LLD

RSTW1

SSC

TEST

RE1

RE2

BLND

ALE

WRD

P0

P1

P2

P3

V

SS1

V

DD2

V

DD4

V

SS3

PORT 3

ALTERNATE

FUNCTIONS

RXD

PROG/ALE

PSEN

VPP/EA

XT

AL2

XT

AL1

RST

TXD

INT0

INT1

T0

T1

WR

RD

PORT 2

PORT 1

PORT 0

ADDRESS AND

DATA BUS

ADDRESS BUS

SDA

SCL

VCC

VSS

7

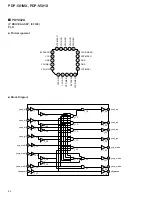

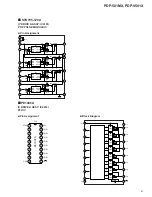

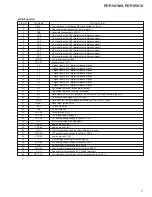

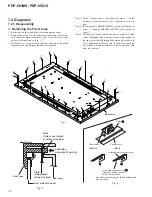

PE6001A9

(PROGRESSIVE BLOCK : IC4720)

PROGRESSIVE ONE TIME µ-COM

¶

Block Diagram

¶

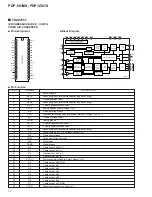

Pin Assignment

7

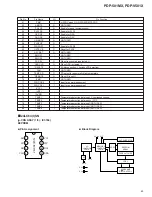

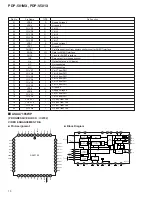

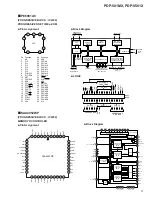

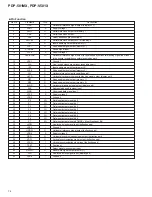

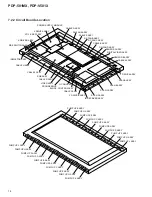

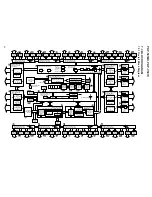

SAA4952WP

(PROGRESSIVE BLOCK : IC4704)

MEMORY OCONTROLER

¶

Block Diagram

¶

Pin Assignment

¶

LOGIC

Summary of Contents for PDP-501MX

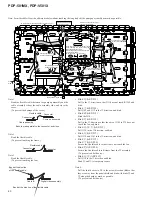

Page 16: ...PDP 501MX PDP V501X 16 A B C D 1 2 3 4 1 2 3 4 3 3 POWER SUPPLY MODULE 1 2 J 1 2 ...

Page 17: ...PDP 501MX PDP V501X 17 A B C D 5 6 7 8 5 6 7 8 J 1 2 ...

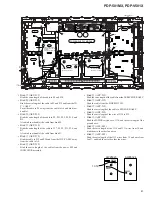

Page 18: ...PDP 501MX PDP V501X 18 A B C D 1 2 3 4 1 2 3 4 3 4 POWER SUPPLY MODULE 2 2 J 2 2 ...

Page 19: ...PDP 501MX PDP V501X 19 A B C D 5 6 7 8 5 6 7 8 J 2 2 ...