PDP-5050SX

178

1

2

3

4

1

2

3

4

C

D

F

A

B

E

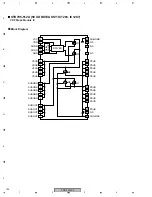

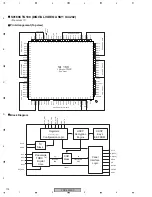

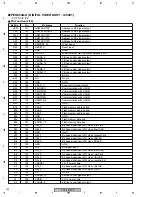

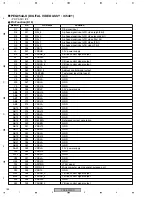

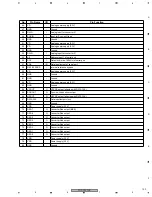

SII169CTG100 (DIGITAL VIDEO ASSY: IC4202)

RESET#

1

SiI 169

100-pin TQFP

(Top View)

PD#

2

SDA

3

PIXS

4

GND

5

VCC

6

STAG_OUT

7

SCDT

8

PDO#

9

QE0

10

QE1

11

QE2

12

QE3

13

QE4

14

QE5

15

QE6

16

QE7

17

OVCC

18

OGND

19

QE8

20

QE9

21

QE10

22

QE11

23

QE12

24

QE13

25

QE14

26

QE15

27

OGND

28

OVCC

29

QE16

30

QE17

31

QE18

32

QE19

33

QE20

34

QE21

35

QE22

36

QE23

37

VCC

38

GND

39

HS_DJTR

40

OCK_INV

41

CTL3

42

OVCC

43

ODCK

44

OGND

45

DE

46

VSYNC

47

HSYNC

48

QO0

49

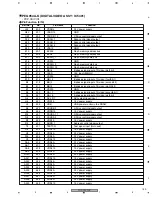

QO1

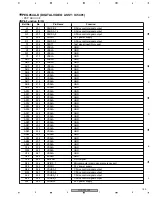

50

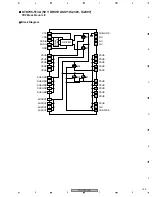

75

QO21

74

QO20

73

QO19

72

QO18

71

QO17

70

QO16

69

GND

68

VCC

67

QO15

66

QO14

65

QO13

64

QO12

63

QO11

62

QO10

61

QO9

60

QO8

59

OGND

58

OVCC

57

QO7

56

QO6

55

QO5

54

QO4

53

QO3

52

QO2

51

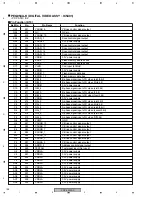

QO22

SCL

100

RESERVED

9

9

PGND

9

8

PVCC

97

EXT_RES

9

6

AVCC

95

RXC-

9

4

RXC+

9

3

AGND

9

2

RX0-

9

1

RX0+

90

AGND

8

9

AVCC

88

AGND

87

RX1-

8

6

RX1+

85

AVCC

84

AGND

8

3

AVCC

82

RX2-

8

1

RX2+

80

AGND

7

9

OVCC

7

8

QO23

7

7

OGND

7

6

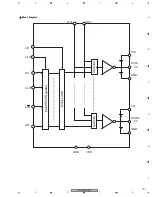

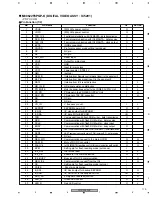

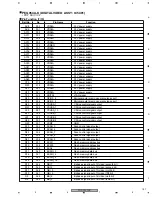

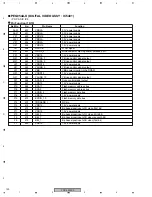

DIFFERENTIAL SIGNALS

ODD 8-bits RED

EVEN 8-bits RED

ODD 8-bits GREEN

EVEN 8-bits GREEN

ODD 8-bits BLUE

EVEN 8-bits BLUE

CONFIG. PINS

PLL

OUTPUT

CLOCK

CONTROLS

Registers

--------------

Configuration Logic

Panel

Interface

Logic

EXT_RES

PanelLink

TMDS

TM

Digital

Core

QE[23:0]

SCLS

SCDT

ODCK

DE

XOR

Mask

RX1

±

RX0

±

RXC

±

RX2

±

QO[23:0]

HSYNC

VSYNC

CTL3

I

2

C

Slave

SDAS

STAG_OUT

PIXS

OCK_INV

HS_DJTR

HDCP

Keys

E EPROM

RESET#

24

/

encrypted

data

24

/

unencrypted

data

control

PD#

PDO#

HDCP

Decryption

Engine

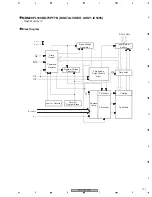

• Receiver IC

Pin Arrangement (Top view)

Block Diagram