PDP-5050SX

198

1

2

3

4

1

2

3

4

C

D

F

A

B

E

77

DSCL

81

EXT_RES

Q[23-0]

76

DSDA

72

71

75

74

RESET#

INT

CSDA

CSCL

26

MCLKOUT

27

MCLKIN

32

SCK

35

DE

33

HSYNC

34

VSYNC

46

ODCK

12

AnGY

7

AnRPr

15

9

AnBPb

RSET

8

COMP

31

WS

30

SDO

29

SPDIF

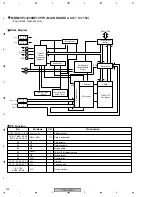

I2C

SLAVE

XOR

MASK

MODE

CONTROL

AUX DATA

LOGIC

BOARD

AUDIO

DATA

DECODE

LOGIC

BOARD

VIDEO

COLOR

SPACE

CONVERTER

UP/DOWN

SAMPLING

HDCP

DECRYPTION

ENGINE

HDCP

KEYS

EEPROM

MCLK

GEN

VIDEO

DAC

PANEL LINK

TMDS

DIGITAL CORE

REGISTERS

CONFIGURATION

LOGIC BLOCK

TM

I2C

SLAVE

CONTROL SIGNALS

CONTROL SIGNALS

36-39,42-44,48-55,

58-63,68-70

RXC

±

83,84

RX0

±

86,87

RX1

±

91,92

RX2

±

96,97

DACVCC

1

N/C

2 DACGND

3

N/C

4

DACGNDR

5

DACVCCR

6

AnRPr

7

COMP

8

RSET

9

DACGNDG

10

DACVCCG

11

AnGY

12

DACGNDB

13

DACVCCB

14

AnBPb

15

GND

16

VCC

17

RSVDL

18

RSVDO

19

RSVDO

20

OVCC

21

PGND2

22

PVCC2

23

PLLIN

24

PLLOUT

25

MCLKOUT

MCLKIN

OGND

SPDIF

SDO

WS

SCK

HSYNC

VSYNC

DE

Q23

Q22

Q21

Q20

Q19

Q18

Q17

OGND

ODCK

OVCC

Q16

Q15

Q14

GND

VCC

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

27

26

75

Q1

74

OVCC

73

CSDA

72

Q3

71

Q4

70

Q5

69

Q6

68

Q7

67

Q8

66

OGND

65

OVCC

64

Q9

63

Q10

62

Q11

61

Q12

60

Q13

59

58

57

56

55

54

53

52

51

Q0

100

DSDA

DSCL

OGND

PGND1

PVCC1

EXT_RES

AVCC

RXC-

RXC+

AGND

RX0-

RX0+

AGND

AVCC

AGND

RX1-

RX1+

AVCC

AGND

AVCC

RX2-

RX2+

AGND

GND

VCC

CSCL

RSVDL

Q2

RESET#

INT

OGND

VCC

GND

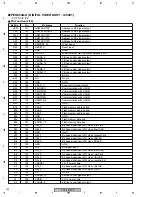

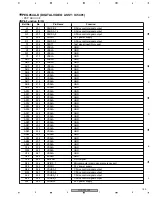

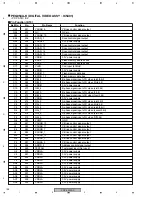

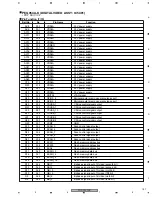

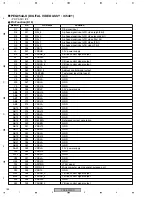

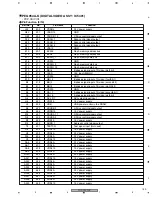

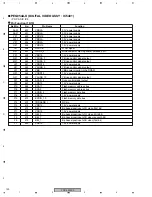

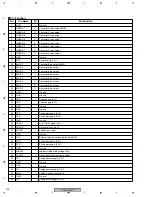

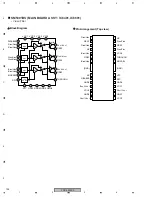

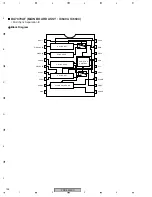

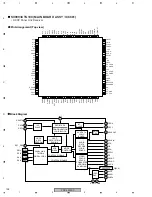

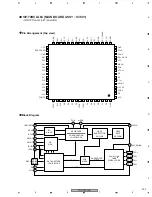

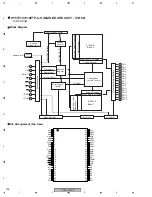

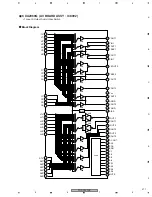

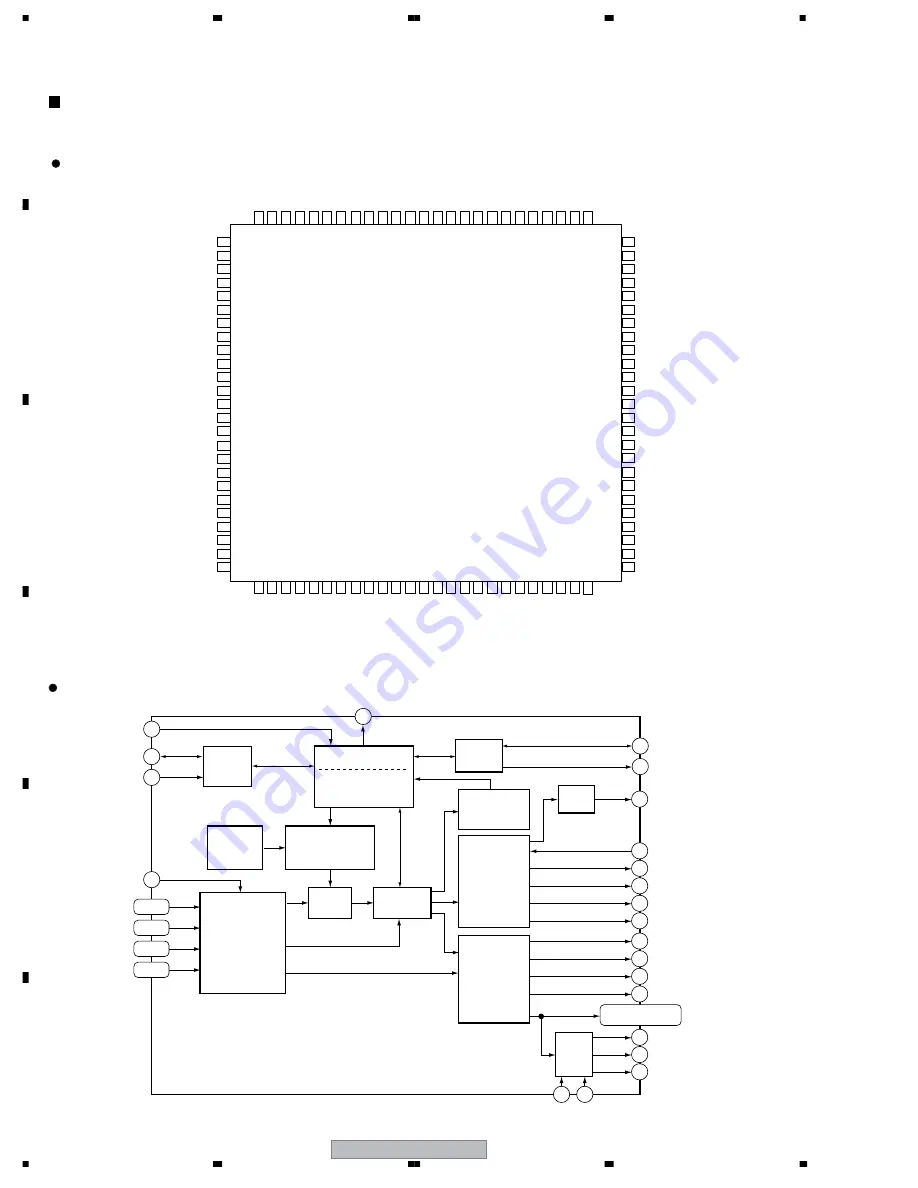

SII9993CTG100 (MAIN BOARD ASSY : IC6881)

• HDCP Panel Link Receiver

Pin Arrangement (Top view)

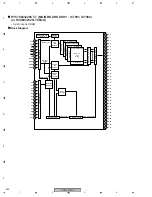

Block Diagram