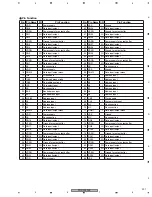

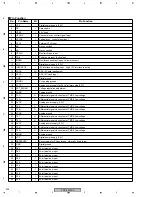

PDP-5050SX

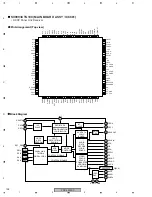

203

5

6

7

8

5

6

7

8

C

D

F

A

B

E

15

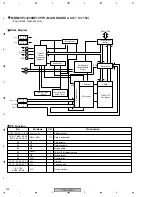

SCLS

4

HSYNC

5

VSYNC

57

IDCK+

56

IDVK-

D[23-0]

2

DE

6

CTL3

14

SDAS

13

10

11

9

19

ISEL/RST#

PD#

MSEN

HTPLG

EXT_SWING

TXC

±

TX0

±

TX1

±

TX2

±

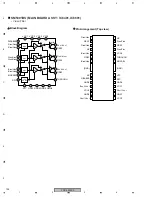

I2C

SLAVE

DE

GEN

XOR

MASK

HDCP

ENCRYPTION

ENGINE

HDCP

KEYS

EEPROM

PANEL LINK

TMDS

DIGITAL CORE

DATA CAPTURE

LOGIC BLOCK

REGISTERS

CONFIGURATION

LOGIC BLOCK

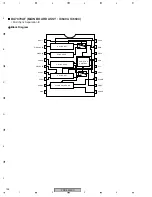

TM

V C C

D E

V R E F

V S Y N C

N C

N C

P D #

V C C

S D A S

S C L S

G ND

PGND1

PVCC1

EXT_SWING

AGND

TXC-

TXC+

AVCC

TX0-

TX0+

AGND

TX1-

TX1+

AVCC

TX2-

TX2+

V C C

G ND

PVCC2

D11

D10

D9

D8

D7

D6

IDCK-

IDCK+

D5

D4

D3

D2

D1

D0

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

AGND

ISEL/RST#

M S E N

H T P L G

C T L 3

H S Y N C

P G N D 2

D 1 2

D 1 3

D 1 4

D 1 5

D 1 6

D 1 7

D 1 8

D 1 9

D 2 0

D 2 1

D 2 2

D 2 3

R E S E R V E D

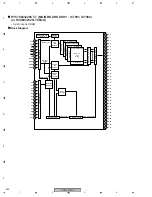

CLEAR DATA

CONTROL SIGNALS

ENCRYPTED

DATA

36-47,

50-55,

58-63

21,22

24,25

27,28

30,31

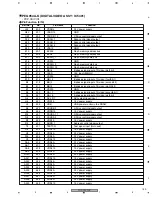

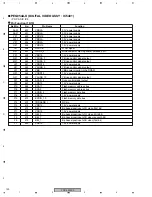

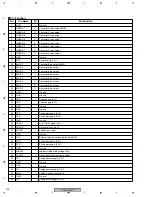

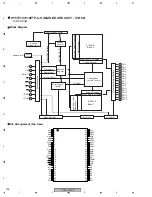

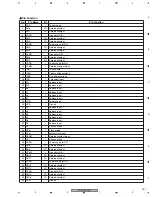

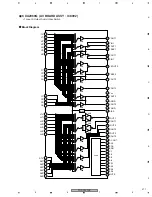

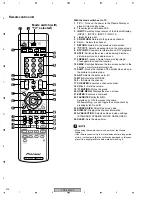

SII170BCLG64 (MAIN BOARD ASSY : IC7401)

• HDCP Panel Link Transmitter

Pin Arrangement (Top view)

Block Diagram