PDP-5050SX

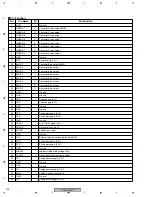

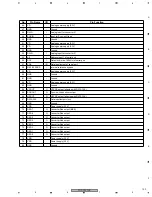

206

1

2

3

4

1

2

3

4

C

D

F

A

B

E

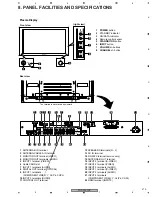

Burst Length

Counter

Refresh

Interval Timer

Refresh

Counter

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

Address

Register

I/O Control

Test Mode

Mode Register

Self Refresh Counter

Column Decoder

Sense AMP & I/O gates

512Kx16

Bank 0

Column Decoder

r

Sense AMP & I/O gates

RAS

CAS

CS

WE

UDQM

LDQM

CKE

Precharge

Overflow

Column Active

Row Active

Address[0:10]

CLK

BA(A11)

State Machine

Row Decoder

Row Addr. Latch/Predecoder

Auto/Self Refresh

Ref. Addr.[0:11]

Data Input/Output Buffe

rs

Row Addr. Latch/

Predecoder

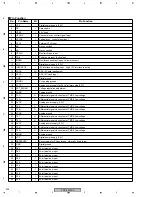

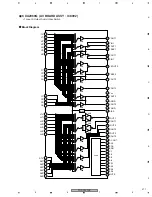

35

2

3

5

6

8

9

11

12

39

40

42

43

45

46

48

49

34

19

18

17

16

15

36

14

21-24,

27-32, 20

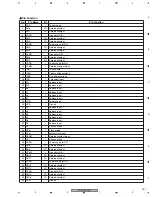

V

DD

1

DQ0

2

DQ1

3

V

SSQ

4

DQ2

5

DQ3

6

V

DDQ

7

DQ4

8

DQ5

9

V

SSQ

10

DQ6

11

DQ7

12

V

DDQ

13

LDQM

14

WE

15

CAS

16

RAS

17

CS

18

A11

19

A10

20

A0

21

A1

22

A2

23

A3

24

V

DD

25

50

V

SS

49

DQ15

48

DQ14

47

V

SSQ

46

DQ13

45

DQ12

44

V

DDQ

43

DQ11

42

DQ10

41

V

SSQ

40

DQ9

39

DQ8

38

V

DDQ

37

NC

36

UDQM

35

CLK

34

CKE

33

NC

32

A9

31

A8

30

A7

29

A6

28

A5

27

A4

26

V

SS

512Kx16

Bank 1

Column Addr.

Latch & Counter

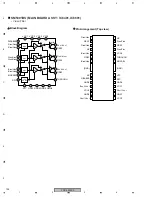

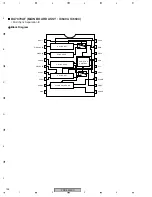

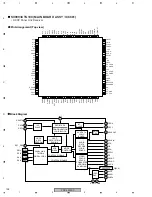

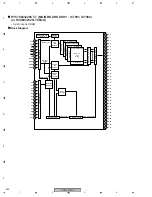

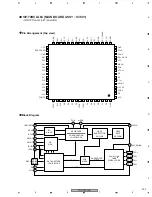

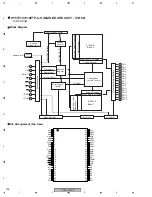

HY57V161610ETP-8-K (MAIN BOARD ASSY : IC6106)

• 16M SDRAM

Block Diagram

Pin Arrangement (Top view)