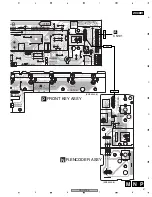

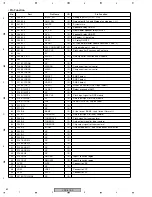

VSX-515-K

61

5

6

7

8

5

6

7

8

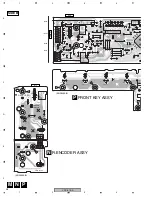

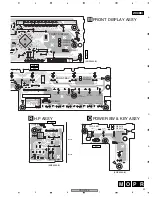

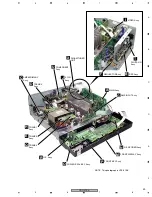

C

D

F

A

B

E

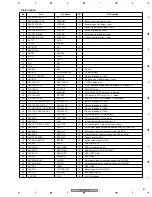

No.

Port

Pin Name

I/O

Pin Function

1

P96/ANEX1/SOUT4

NC

I/O

2

P95/ANEX0/CLK4

DISP RST

I/O

Reset signal to display u-com

3

P94/DA1/TB4IN

DISP EN

I/O

Enable signal to display u-com

4

P93/DA0/TB3IN

DISP RDY

I/O

Ready signal from display u-com

5

P92/TB2IN/SOUT3

DISP DI

I/O

Data out to display u-com

6

P91/TB1IN/SIN3

DISP DO

I/O

Data input from display u-com

7

P90/TB0IN/CLK3

DISP CLK

I/O

Clock signal to display u-com

8

BYTE

GND

9

CNVss

CNVSS

10

P87/XCIN

NC

I/O

11

P86/XCOUT

NC

I/O

12

RESET

XRESET

13

XOUT

XOUT

14

VSS

GND

15

XIN

XIN

16

VCC

5V

17

P85/NMI

NM

I

No use

18

P84/INT2

ACIN(WAKEUP)

I/O

AC pulse input

19

P83/INT1 P85/NMI

1394 INT

I/O

No use (Standby for 1394)

20

P82/INT0

1W WUP

I/O

Wake up signal from display u-com

21

P81/TA4IN/U

DECO MUTE

I/O

1st DSP detect port

22

P80/TA4OUT/U

NECK_SEL

I/O

5.1ch, surround mode and A+B Stereo : H / Stereo : L

23

P77/TA3IN

DC PROT

I/O

AMP DC detect

24

P76/TA3OUT

Boad DET

I/O

AMP INPUT ASSY detect, H : detected

25

P75/TA2IN/W

MIC DET

I/O

MIC detect (VSX-D914 only), L : detect

26

P74/TA2OUT/W

DSP OL

I/O

ANALOG OVER LOAD detect, H : detected

27

P73/CTS2/RTS2/TA1IN/V

NC(1394 CS)

I/O

No use (Standby for 1394)

28

P72/CLK2/TA1OUT/V

NC(1394 CK)

I/O

No use (Standby for 1394)

29

P71/RxD2/SCL/TA0IN/TB5IN

NC(1394 DO)

I/O

No use (Standby for 1394)

30

P70/TXD2/SDA/TA0OUT

NC(1394 DI)

I/O

No use (Standby for 1394)

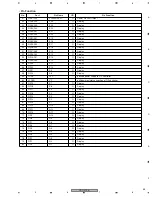

31

P67/TXD1

232C RXD

I/O

For rewriting 232C (Data output)

32

P66/RxD1

232C TXD

I/O

For rewriting 232C (Data input)

33

P65/CLK1

CLK

I/O

It is necessary when writing for JIG

34

P64/CTS1/RTS1/CLKS1

232C CTS

I/O

For rewriting 232C (Admit communication)

35

P63/TXD0

DSP DI

I/O

Data output signal for communication with DSP and DIR

36

P62/RxD0

DSP DO

I/O

Data input signal for communication with DSP

37

P61/CLK0

DSP CLK

I/O

Clock signal for communication with DSP and DIR

38

P60/CTS0/RTS0

DSP RST

I/O

Reset signal for DSP

39

P57/RDY/CLKOUT

DSP SS

I/O

Srobe select signal to DSP

40

P56/ALE

BUSY

I/O

Use it in MCACC

41

P55/HOLD

DSP HREQ

I/O

DSP error detect signal

42

P54/HLDA

DSP MODE

I/O

Mode select of DSP (ROM/RAM)

43

P53/BCLK

DSP MUTE

I/O

DSP ASSY mute

44

P52/RD

ADMODE

0

DSP ASSY

45

P51/WRH/BHE

DIR DO

I/O

Data input signal for communication with DIR/DAC

46

P50/WRL/WR

DIR CS

I/O

Chip select signal for communication with DIR/DAC

47

P47/CS3

LSSN

0

DSP ASSY

48

P46/CS2

DIR CDC RST

I/O

Reset signal for DIR CODEC

49

P45/CS1

DIR ERR

I/O

lock/unlock signal

50

P44/CS0

XTL0

I/O

DIR X'tal change

• Pin Function