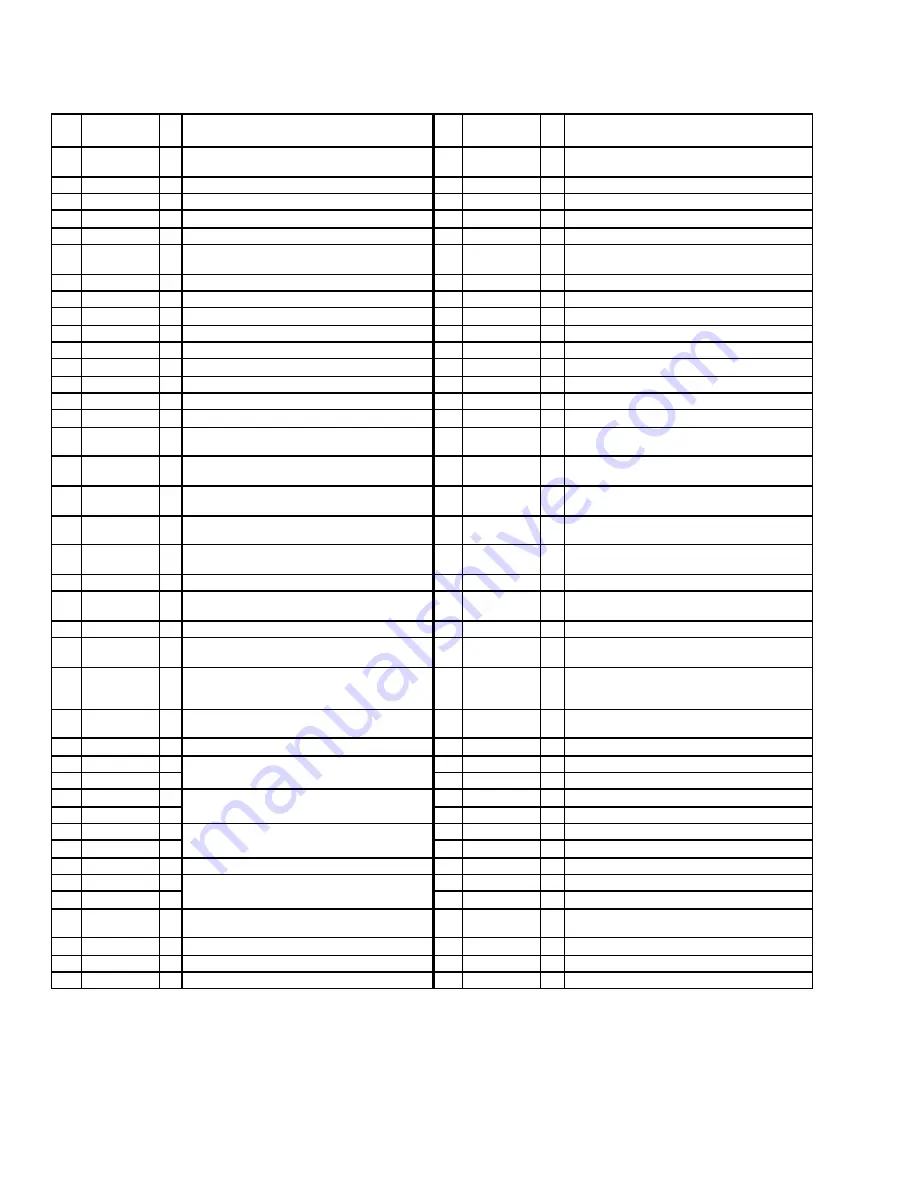

80

XC-IS21MD

¡N-

o.

Pin Name

I/O

Function

No.

Pin Name

I/O

Function

1

SQSO

O

SubQ 80-bit, PCM peak and level data output

CD TEXT data output

41

TE

I

Tracking error input

2

SQCK

I

Clock input for SQSO readout

42

CE

I

Center servo analog input

3

XRST

I

System reset Reset when "L"

43

RFDC

I

RF signal input

4

SYSM

I

Mute input Mute when "H"

44

ADIO

O

OP amplifier output

5

DATA

I

Serial data input from CPU

45

AV

SS

0

−

Analog GND

6

XLAT

I

Latch input from CPU

Serial data is latched at the falling edge.

46

IGEN

I

Constant current input for OP amplifier

7

CLOK

I

Serial data transfer clock input from CPU

47

AV

DD

0

−

Analog power supply

8

SENS

O

SENS output to CPU

48

ASYO

O

EFM full-swing output ("L"=VSS, "H"=VDD)

9

SCLK

I

Clock input for SENS serial-data readout

49

ASYI

I

Asymmetry comparate voltage input

10

V

DD

−

Digital power supply

50

BIAS

I

Constant current input of the asymmetry circuit

11

ATSK

I/O Input and output for unti-shock

51

RFAC

I

EFM signal input

12

SPOA

I

Microcomputer extended interface (input A)

52

AV

SS

3

−

Analog GND

13

SPOB

I

Microcomputer extended interface (input B)

53

CLTV

I

VCO control voltage input for master

14

XLON

O

Microcomputer extended interface (output)

54

FILO

O

Filter output for master PLL (Slave=digital PLL)

15

WFCK

O

WFCK output

55

FILI

I

Filter input for master PLL

16

XUGF

O

XUGF output MNT1 and RFCK output by

switching the command.

56

PCO

O

Charge pump output for master PLL

17

XPCK

O

XPLCK output MNT0 output by switching the

command.

57

AV

DD

3

−

Analog power supply

18

GFS

O

GFS output MNT3 and XRAOF output by

switching the command.

58

V

SS

−

Digital GND

19

C2PO

O

C2PO output GTOP output by switching the

command.

59

V

DD

−

Digital power supply

20

SCOR

O

Outputs "H" when either subcode sync. S0 or S1 is

detected.

60

DOUT

O

DIGITAL OUT output

21

COUT

I/O Input and output of track-number count signal

61

LRCK

O

D/A interface LR clock output f=Fs

22

MIRR

I/O Mirror signal input and output

62

PCMD

O

D/A interface

Serial data output (two's complement, MSB first)

23

DFCT

I/O Defect signal input and output

63

BCK

O

D/A interface Bit clock output

24

FOK

I/O Focus OK signal input and output

64

EMPH

O

Outputs "H" when the playback disc has emphasis,

and "L" when there is no emphasis.

25

LOCK

I/O

GFS is sampled at 460Hz;when GFS is "H", this pin

outputs "H". If GFS is "L" eight consecutive

samples, this pin outputs "L". Input when LKIN="H".

65

XV

DD

−

Power supply for master clock

26

MDP

O

Servo control output of spindle motor

66

XTAI

I

Crystal oscillation circuit input

Input the external master clock via this pin.

27

SSTP

I

Detection signal input of disc innermost

67

XTAO

O

Crystal oscillation circuit output

28

SFDR

O

Sled drive output

68

XV

SS

−

GND for master clock

29

SRDR

O

69

AV

DD

1

−

Analog power supply

30

TFDR

O

Tracking drive output

70

AOUT1

O

L ch analog output

31

TRDR

O

71

AIN1

I

L ch OP amp. input

32

FFDR

O

Focus drive output

72

LOUT1

O

L ch LINE output

33

FRDR

O

73

AV

SS

1

−

Analog GND

34

V

SS

−

Digital GND

74

AV

SS

2

−

Analog GND

35

TEST

I

TEST pin : normally GND

75

LOUT2

O

R ch LINE output

36

TEST

I

76

AIN2

I

R ch OP amp. input

37

XTSL

I

Crystal selector input

"L":16.9344MHz , "H":33.8688MHz

77

AOUT2

O

R ch analog output

38

VC

I

Center voltage input

78

AV

DD

2

−

Analog power supply

39

FE

I

Focus error signal input

79

RMUT

O

R ch zero detection flag

40

SE

I

Sled error signal input

80

LMUT

O

L ch zero detection flag

•

Pin Function

Notes)

• PCMD is an MSB first. two's complement output.

• GTOP is used to monitor the frame sync protection status. (High:sync protection window released)

• XUGF is the negative pulse for the frame sync derived from the EFM signal. It is the signal before sync protection.

• XPLCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge of XPLCK and the EFM signal transition point coincide.

• GFS goes high when the frame sync and the insertion protection timing match.

• RFCK is derived with the crystal accuracy. This signal has a cycle of 136

µ

s.

• C2PO represents the data error status.

• XRAOF is generated when the 16K RAM exceeds the

±

4F jitter margin.