EL640.200-SK Operations Manual (020-0348-00B)

10

Video Input Signals

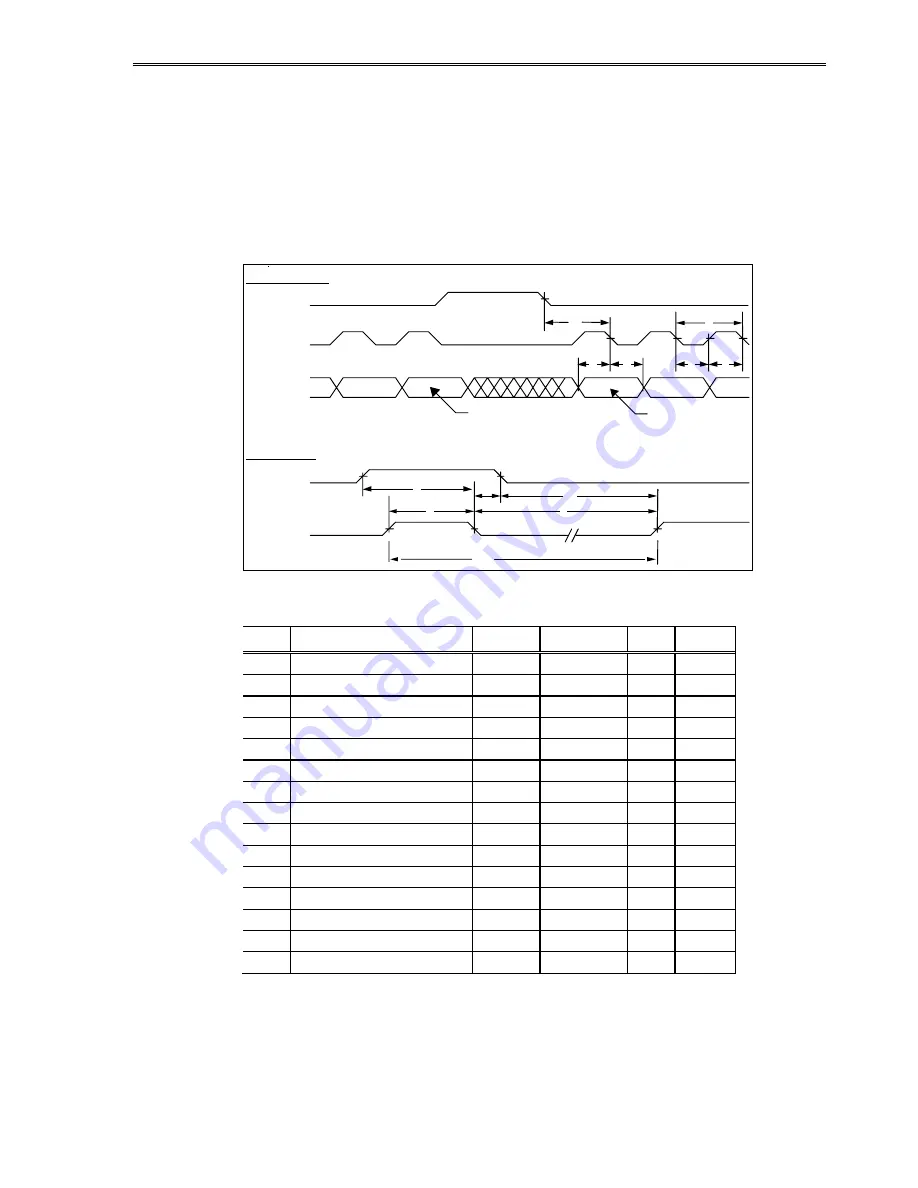

The end of the top line of a frame is marked by VS, vertical sync signal as

shown in Figure . The end of each row of data is marked by HS. In non-buffered

mode, the VS signal may be independently set to a CMOS low level at any time

for longer than one frame period. During the time of VS inactivity the display is

blank. Halting VS results in a standby condition to minimize power usage in

buffered mode.

HS

VCLK

VID0-3

VS

HS

3

First Line VID

4

1

Pixels: w x y z

Horizontal Timing

Vertical Timing

Pixels: a b c d

5

6

9

10

7

11

8

2

Second Line VID Data

12

Figure 3. Video Input Timing Diagram.

Table 5. Video Input Descriptions.

Num Description

Symbol

Min.

Max.

Units

1

HS high time

tHSh

125

nsec

2

HS low time

tHSl

160

tVCLK

3

HS to VCLK

tHSsu

63

nsec

4

VID setup to VCLK

tVIDsu

100

nsec

5

VID hold from VCLK

tVIDhd

100

nsec

6

Video clock period

tVCLK

334 (200*)

nsec

VCLK rise, fall time

tVCLKrf

50

nsec

7

VCLK low width

tVCLKl

125

nsec

8

VCLK high width

tVCLKh

125

nsec

9

VS high setup to HS low

tVShsu

100

nsec

10

VS hold after HS

tVShd

100

nsec

11

VS low setup to HS high

tVSlsu

140

nsec

12

HS period

tHS

53.6 (41.3*)

µsec

VS period

tVS

200 (101*)

tHS

Max frame rate*

239*

Hz

* Non-buffered mode