MC100LVEP111

Pair 0

Pair 1

Pair 2

Pair 3

Pair 4

Pair 5

CY28400-2

Pair 1

Pair 2

Pair 5

NB3N5573

2

U108

U61

Pair 1

Pair 2

Pair 5

Source

Termination

Source

Termination

Source

Termination

U28

CY28400-2

From 4x PCI

Express

Cable

Connector

J5

PEX

8619

C

CFC_REFCK

REFCK

C

C

C

C

U113

Pair 6

Pair 7

Pair 8

Pair 9

MC100LVEP111

Pair 0

Pair 1

Pair 2

Pair 3

Pair 4

Pair 5

U114

Pair 6

Pair 7

Pair 8

Pair 9

Source

Termination

Source

Termination

Source

Termination

Voltage

Devider

Voltage

Devider

Pos1/SW6

0

1

SEL

Voltage

Devider

Voltage

Devider

0

1

SEL

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

Source

Termination

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

Voltage

Devider

Voltage

Devider

Voltage

Devider

Voltage

Devider

Voltage

Devider

Voltage

Devider

SLOT 1

SLOT 2

SLOT 3

SLOT 4

SLOT 5

Voltage

Devider

Voltage

Devider

Voltage

Devider

Voltage

Devider

Voltage

Devider

SLOT 6

SLOT 7

SLOT 8

SLOT 9

SLOT 10

Voltage

Devider

Voltage

Devider

Voltage

Devider

Voltage

Devider

Voltage

Devider

SLOT 11

SLOT 12

SLOT 13

SLOT 14

SLOT 15

JP100

Refclk header for

Midbus probe

SSC_ISO_EN_n

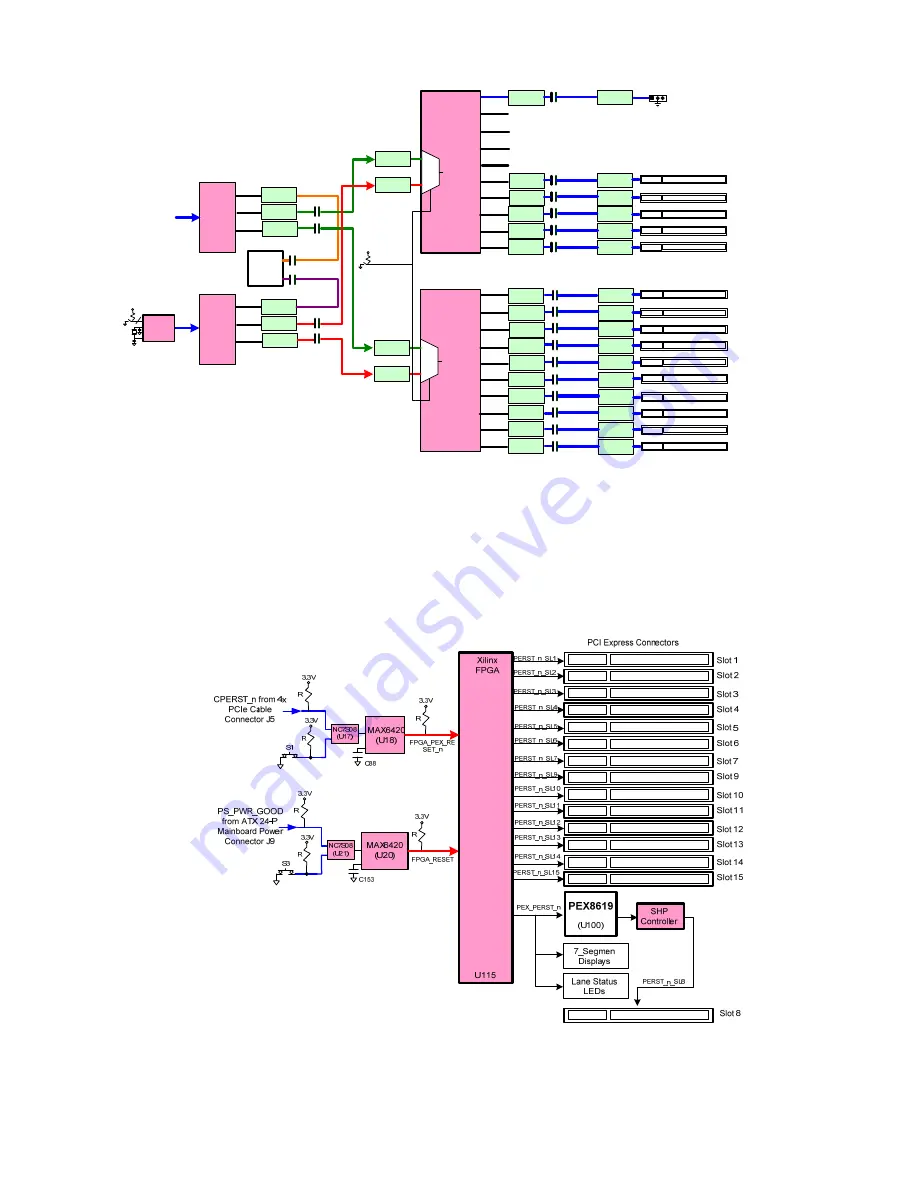

Figure 8. RDK Reference Clock Circuits

3.4

Reset Circuits

Refer to

, the RDK reset circuits include two National NC7S08 2-input AND gate (U17&U21), two Maxim

MAX6420 reset controllers (U18 and U20), one Xilinx FPGA (U115), a Serial Hot-Plug controller, momentary

switches (S1 and S3), resistors and capacitors.

Figure 9. RDK Reset Circuits

PEX 8619BA Base Board RDK Hardware Reference Manual – Version 1.0

Copyright © 2008 by PLX Technology, Inc. All rights reserved

9