PMC-941028 (R4)

©

1998 PMC-Sierra, Inc. September, 1998

PM7344

PMC-Sierra,Inc.

Quad T1/E1 Multi-PHY SATURN User Network Interface

S/UNI-MPH

FEATURES

• Monolithic single-chip quad ATM

Physical Layer User Network Interface

(UNI) operating at 1.544 Mbit/s or

2.048 Mbit/s.

• Integrates a quad full-featured dual-

mode T1/E1 framer/transmitter for

terminating four duplex 1.544 Mbit/s

DS1 or four duplex 2.048 Mbit/s E1

signals. Recovers T1/E1 clock and

data using a digital phase locked loop

for high jitter tolerance.

• Implements the ATM Forum UNI

Specification V3.1 for DS1 and E1

transmission rates.

• Implements the ATM physical layer for

Broadband ISDN according to ITU-T

Recommendation I.432.

• Implements direct mapping into four T1

or E1 streams according to ITU-T

Recommendation G.804.

• Provides UTOPIA L1-compliant,

UTOPIA L2-compatible ATM-PHY

interface with parity and multi-PHY

control signals.

• Software-compatible with the

PM4341A T1XC, PM6341 E1XC,

PM4351 COMET, PM5346 S/UNI

®

-

LITE and PM7345 S/UNI-PDH.

• Application-compatible with the

PM8313 D3MX, PM4314 QDSX, and

PM7323 RCMP-200.

• Provides a generic 8-bit

microprocessor bus interface for

configuration, control, and status

monitoring.

• Low power, +5 V, CMOS technology.

• Packaged in a 128-pin rectangular

(14 mm by 20 mm) PQFP package.

T1 FRAMER/TRANSMITTER

• Supports SF or ESF format signals

using B8ZS or AMI line code.

• Provides Loss Of Signal (LOS)

detection and red, yellow and Alarm

Indication Signal (AIS) alarm detection.

Supports transmission of (AIS) or

yellow alarm signal in all formats.

• Detects violations of the ANSI T1.403

12.5% pulse density rule over a

moving 192-bit window.

• Supports line and path performance

monitoring according to ANSI

specifications. Accumulators are

provided for counting ESF CRC-6

errors, framing bit errors, LCVs, and

LOF, or frame alignment events.

• Provides ESF bit-oriented code

detection/generation, and an HDLC

interface for terminating/generating the

ESF datalink.

• Extracts/inserts the datalink in ESF

mode.

E1 FRAMER/TRANSMITTER

• Supports G.704 2048 kbit/s format

using HDB3 or AMI line coding.

• Supports CRC multiframe alignment or

the signalling multiframe alignment.

• Declares red and AIS alarms using

Q.516 recommended integration

periods. Provides LOS detection, and

indicates loss of frame alignment

(OOF), loss of signalling, and loss of

CRC multiframe alignment.

• Supports line and path performance

monitoring according to ITU-T

recommendations. Accumulators are

provided for counting CRC-4 errors,

FEBE, frame sync errors, and LCVs.

• Supports reception and transmission

of remote alarm and AIS.

• Provides an HDLC interface for

terminating/generating a datalink.

• Supports the timeslot 16 (64 kbit/s)

datalink which may be used for

common channel signalling, or any

combination of the national bits.

APPLICATIONS

• ATM Switches Supporting DS1 or E1

UNI Ports

• ATM Switches Supporting DS3 or E3

Ports Carrying Multiplexed DS1 or E1

UNI Signals

• ATM Switches Supporting SONET/

SDH Ports Carrying Tributary Mapped

DS1 or E1 UNI Signals

• ATM Customer Premise Equipment

Supporting Multiple DS1 or E1 UNI

Ports

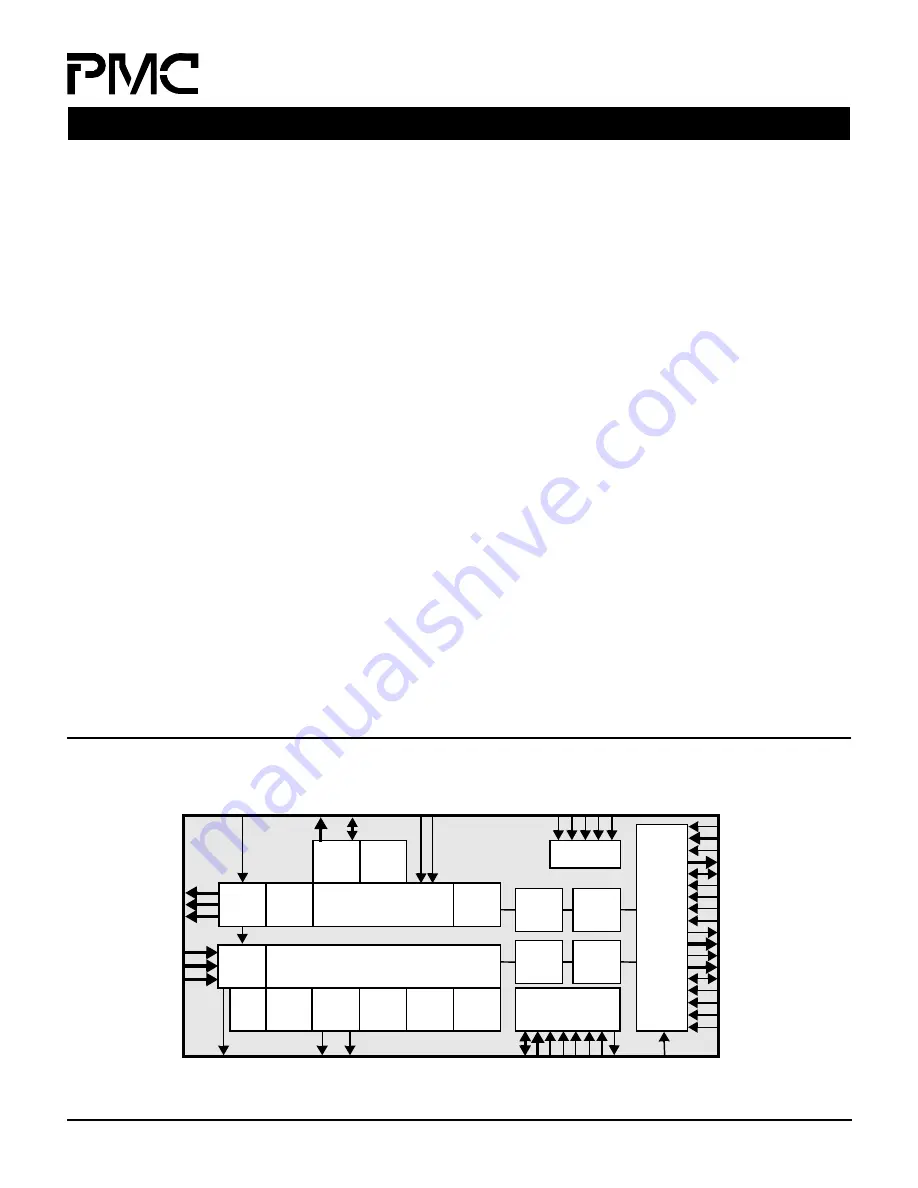

BLOCK DIAGRAM

D[

7:

0]

A

[10:

0]

AL

E

CS

B

WR

B

RDB

IN

T

B

HDLC

Receiver

Microprocessor

Interface

RS

T

B

RCLKI[4:1]

RDP/RDD[4:1]

RDN/RLCV/ROH[4:1]

TCLKO[4:1]

TDP/TDD[4:1]

TDN/TOHO[4:1]

Bit-oriented

Code

Transmitter

HDLC

Transmitter

In-band

Code

Detector

Performance

Monitor

Bit-oriented

Code

Receiver

Alarms

Integrator

XC

L

K

TC

L

K

I

TF

P

I/

T

OH

I

RCLK

O

RDLE

O

M

/

RDL

CLK

[4:1]

T1/E1

Framing Insertion

RDAT[7:0]

RXPRTY

RCA[4:1]

RRDENB[4]/RCAMPH

TWRENB[4]/TCAMPH

TWRENB[3]/TWA[1]

TXPRTY

TCA[4:1]

TSOC

TDAT[7:0]

TWRENB[2]/TWA[0]

TFCLK

RSOC

TWRENB[1]/TWRMPHB

Multi-PHY

Interface

Pulse

Density

Violation

Detector

T1/E1

Framer

Pulse

Density

Enforcer

In-band

Loopback

Code

Generator

Transmit

ATM Cell

Processor

Receive

ATM Cell

Processor

Transmit

ATM 4-Cell

FIFO

Receive

ATM 4-Cell

FIFO

T

D

LUDR/

T

D

LCLK

[4

:1

]

Digital

Receive

Interface

RDLI

N

T

/

RDLS

IG[

4:

1]

MPH

E

N

TD

L

IN

T

/

T

D

L

S

IG

[4

:1

]

RRDENB[3]/RRA[1]

RRDENB[2]/RRA[0]

RRDENB[1]/RRDMPHB

RFCLK

JTAG Test

Access Port

TD

O

TD

I

TC

K

TR

S

T

B

TM

S

Digital

Transmit

Interface