80

Prestigio Cavaliere 141

Technical Service Manual

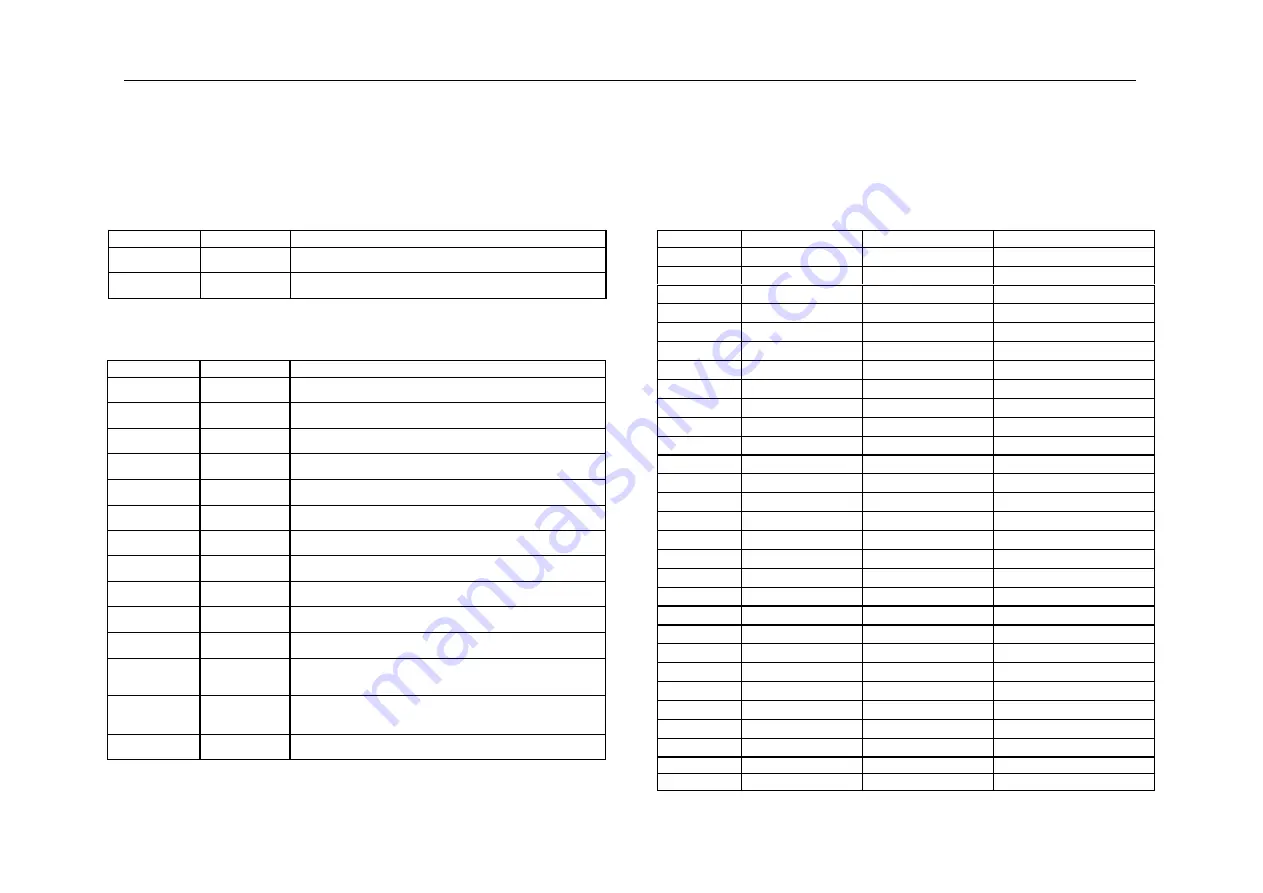

5. Pin Descriptions of Major Components

Hos t BUS Inter face Continue

Na m e

P i n At t r

S i gn a l De s cr i pt i on

HP COM P

I

M

GT L P -M OS Com pensat ion Input

HVREF[4:0]

HNCOM P VREF

I

M

AGT L+ I/O reference volt age

DRAM Contr oller

Na m e

P i n At t r

S i gn a l De s cr i pt i on

SDCLK

I

3.3V - M

SDRAM Clock Input

SDRCLKI

I

2.5V/3.3V - M

SDRAM Read Clock Input

FW DSDCLKO

O

2.5V/3.3V – M

SDRAM Forward Clock Out put

M A[14:0]

O

2.5V/3.3V - M

Sy st em M em ory Address Bus

SRAS#

O

2.5V/3.3V - M

SDRAM Row Address St robe

SCAS#

O

2.5V/3.3V - M

SDRAM Colum n Address St robe

SW E#

O

2.5V/3.3V - M

SDRAM W rit e Enable

CS[5:0]#

CSB[5:0]#

O

2.5V/3.3V - M

SDRAM Chip Select

CSB[5:0] m ult iplexed wit h DQS[5:0]

DQM [7:0]#

O

2.5V/3.3V - M

SDRAM Input /Out p ut Dat a M ask

DQS[7:0]

I/O

2.5V/3.3V - M

DDR Dat a St robe

M D[63:0]

I/O

2.5V/3.3V - M

Sy st em M em ory Dat a Bus

CKE[5:0]

O (open-drain)

2.5V/3.3V –

AUX

SDRAM Clock Enable

S3AUXSW #

(CKE6)

O (open-drain)

2.5V/3.3V -

AUX

Aux power swit ch for ACP I-S3 st at e, low act ive.

DDRVREF[A:B] I

M

DDR I/O Reference Volt age

P ower a n d G r ou n d Sign a ls

Na m e T oler a n ce P ower

P la n e

T yp e

Attr ib u te

C4XAVDD

3.3V MAIN Analog

C4XAVSS 0V

GROUND

Analog

DACAVDD1

1.8V MAIN Analog

DACAVDD2

1.8V MAIN Analog

DACAVSS1

0V GROUND

Analog

DACAVSS2

0V GROUND

Digital

DCLKAVDD

3.3V MAIN Digital

DCLKAVSS

0V GROUND

Analog

DDRAVDD 3.3V

MAIN

Analog

DDRAVSS

0V GROUND

Analog

ECLKAVDD

3.3 MAIN Analog

ECLKAVSS

0V GROUND

Analog

IVDD

1.8V MAIN Digital

OVDD 3.3V

MAIN

Digital

PVDD 3.3V

MAIN

Digital

PVDDM

3.3V AUX Digital

PVDDP

1.8V MAIN Digital

PVDDZ 1.8V

MAIN

Digital

SDAVDD

3.3V MAIN Analog

SDAVSS

0V GROUND

Analog

VDDM

2.5/3.3V MAIN(AUX)

Digital

VDDQ

1.5/1.8/3.3V MAIN

Digitalv

VDDZ

1.8V MAIN Digital

VDDMCMP

1.8V MAIN Analog

VTT

1.2~1.85V MAIN

Digital

Z1XAVDD

3.3V MAIN Analog

Z1XAVSS

0V GROUND

Analog

Z4XAVDD

3.3V MAIN Analog

Z4XAVSS 0V

GROUND

Analog

5.2 SiS650 (IGUI Host Memory Controller )