83

Prestigio Cavaliere 141

Technical Service Manual

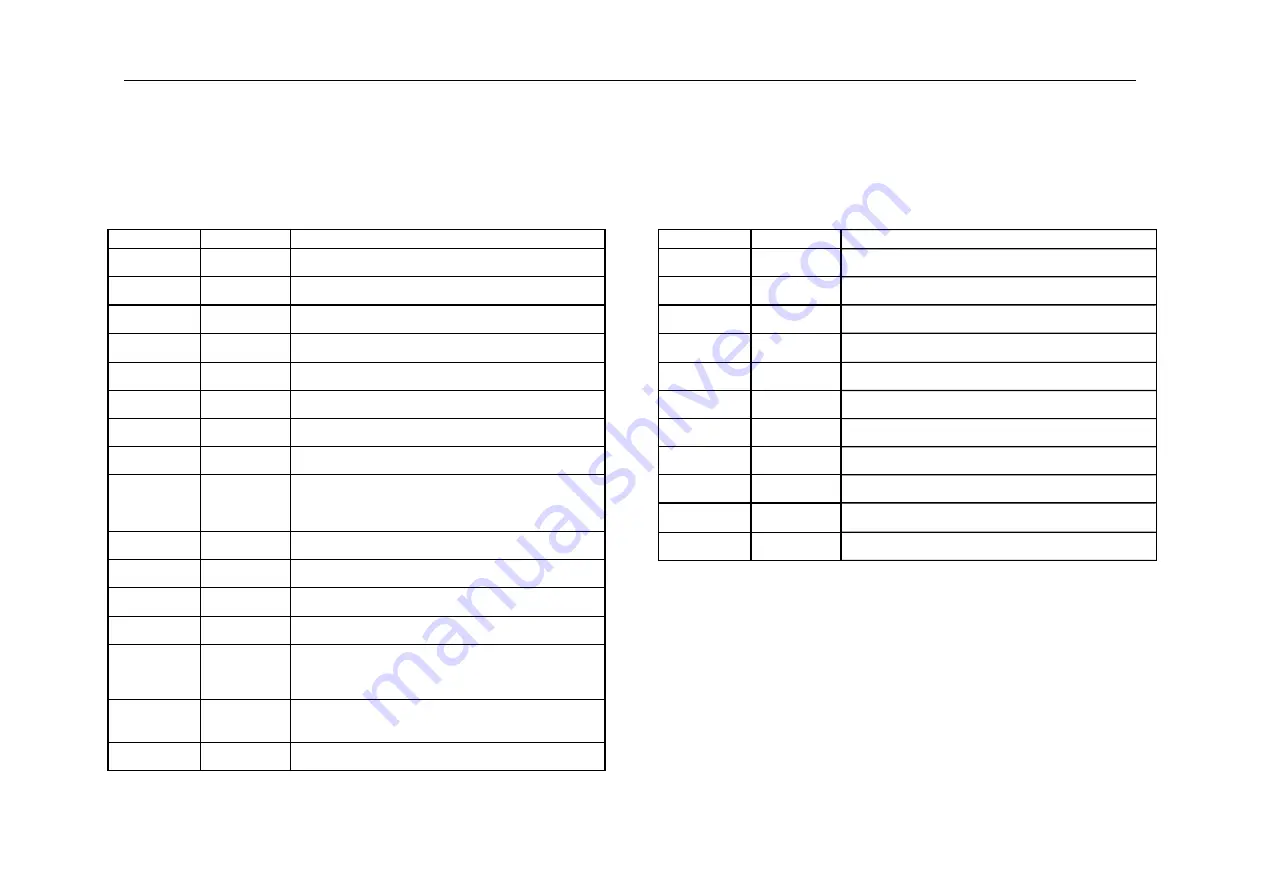

5. Pin Descriptions of Major Components

VB Inter face

Nam e

Pin Attr

Sign al Descr iption

VBCLK

I

1.8V/3.3V - M

Channel B/A Clock Input

VBCLK multiplexed with SBA0

VBHCLK

O

1.8V/3.3V – M

VB Programming Interface Clock

VBHCLK multiplexed with RBF#

VBCAD

I/O

1.8V/3.3V – M

VB Programming Interface Data

VBCAD multiplexed with AREQ#

VBCT L[1:0]

O

1.8V/3.3V - M

VB Data Control

VBCT L[1:0] multiplexed with AAD[29:28]

VGPIO[3:2]

I/O

3.3V - M

VB GPIO pins

VGPIO[3:2] multiplexed with PIPE#/WBF#

VBHSYNC

I/O

1.8V/3.3V - M

Channel B H-Sync

VBHSYNC multiplexed with AAD30

VBVSYNC

I/O

1.8V/3.3V - M

Channel B V-Sync

VBVSYNC multiplexed with AAD31

VBDE

I/O

1.8V/3.3V - M

Channel B Data Valid

VBDE multiplexed with AAD27

VBGCLK

I/O

1.8V/3.3V - M

Channel B Clock Output.

T his clock is used to trigger dual edge data transfer.

Perfect duty cycle is required.

VBGCLK multiplexed with AD_ST B1

VBD[11:0]

I/O

1.8V/3.3V - M

Channel B Data

VBD[11:0] multiplexed with AAD

VAHSYNC

I/O

1.8V/3.3V - M

Channel A H-Sync

VAHSYNC multiplexed with AAD18

VAVSYNC

I/O

1.8V/3.3V - M

Channel A V-Sync

VAVSYNC multiplexed with AAD17

VADE

I/O

1.8V/3.3V - M

Channel A Data Valid

VADE multiplexed with AAD16

VAGCLK

I/O

1.8V/3.3V - M

Channel A Clock Output.

T his clock is used to trigger dual edge data transfer.

Perfect duty cycle is required.

VAGCLK multiplexed with AD_ST B0

VAGCLK#

I/O

1.8V/3.3V - M

Channel A Differential Clock Output. (T o support

Chrontel).

VAGCLK# multiplexed with AD_ST B0#

VAD[11:0]

I/O

1.8V/3.3V - M

Channel A Data

VAD[11:0] multiplexed with AAD

VGA Inter face

Nam e Pin

Attr

Sign al

Descr iption

VOSCI

I

3.3V - M

14.318 Reference Clock Input

HSYNC

O

3.3V - M

Horizontal Sync

VSYNC

O

3.3V - M

Vertical Sync

INT A#

O

3.3V - M

Internal VGA Interrupt Pin

VGPIO[1:0]

I/O

3.3V - M

Internal VGA GPIO pins

VCOMP

AI

Analog - M

Compensation Pin

VRSET

AI

Analog - M

Reference Resistor

VVBWN

AI

Analog - M

Voltage Reference

ROUT

AO

Analog - M

Red Signal Output

GOUT

AO

Analog - M

Green Signal Output

BOUT

AO

Analog - M

Blue Signal Output

5.2 SiS650 (IGUI Host Memory Controller )