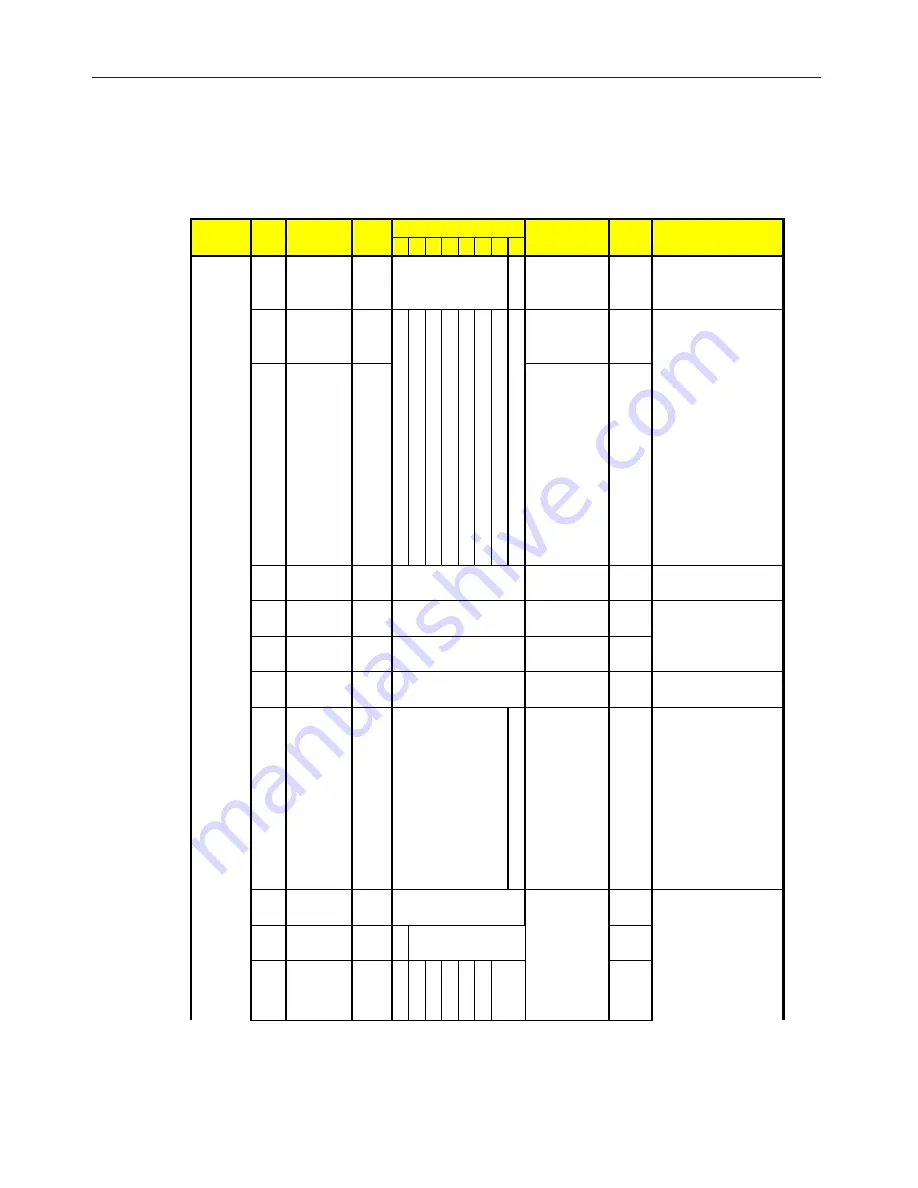

Register

Bit Number

Function Addre

ss

Name

R/W

7 6 5 4 3 2 1 0

Logic

Default Description

A0h

*3

ADP_STS

R(/W)

RES [7:1]

C

O

N

-

-

CON = 1: AC adapter is

connected

A1h

*3

BAT1_STS

(1st Battery)

R(/W)

-

-

A2h

*3

BAT2_STS

(2

nd

Battery)

R(/W)

B

T

P

E

M

P

L

O

W

W

A

R

E

R

R

D

C

H

G

C

H

G

C

O

N

-

-

BTP =1:

EMP =1:

LOW =1:

WAR=1:

ERR =1:

DCHG=1:

CHG=1:

CON=1:

Battery trip

point is

detected.

Battery is

empty.

Battery is Low

battery state.

Battery is

Warning state.

Battery is Error

state.

Battery is

discharged.

Battery is

charged.

Battery is

connected.

A3h

*3

Reserved

R/W

Don

’

t care

-

-

A4h

*3

BAT1_CAP R(/W)

BCAP

-

-

A5h

*3

BAT2_CAP R(/W)

BCAP

-

-

0x00-0x64 = 0-100(%)

0x7F = Unknown

0x80 = Not installed

A6h

*3

Reserved

R/W

Don

’

t care

-

-

A7h

SMB_Alert_

ADDR

R/W

ADDRESS[6:0]

R

E

S

-

0x00

SMBAlert output device

address

The alert response function

is available when this

register is cleared (0x00)

only.

When the several devices

assert the alert signal at the

same time, the least address

is stored to this register.

And when this register is

cleared , next alert address

is stored to this register.

A8h

*5

GPIO-A_

EVT_STS

R/W

STS_A [7:0]

0x00

A9h

*5

GPIO-B_

EVT_STS

R/W

0

STS_B [6:0]

0x00

Status

AAh

*5

GPIO-C_

EVT_STS

R/W

0 0 0 0 0

0

STS

_C

[1:0]

Read

0:No event

1:EVT detection

Write

0:Clear event

1:Ignore

0x00

To clear the notified event

flag without unexpected

event loss, clear the

corresponding bit flag only.

For this operation, this

register has special writing

manner as follows.

STS_X

ß

(STS_X)

AND (Written data)

TECHNICAL SERVICE MANUAL

Prestigio Cavaliere 142

56