LPWA Module Series

BG95 Hardware Design

BG95_Hardware_Design 21 / 80

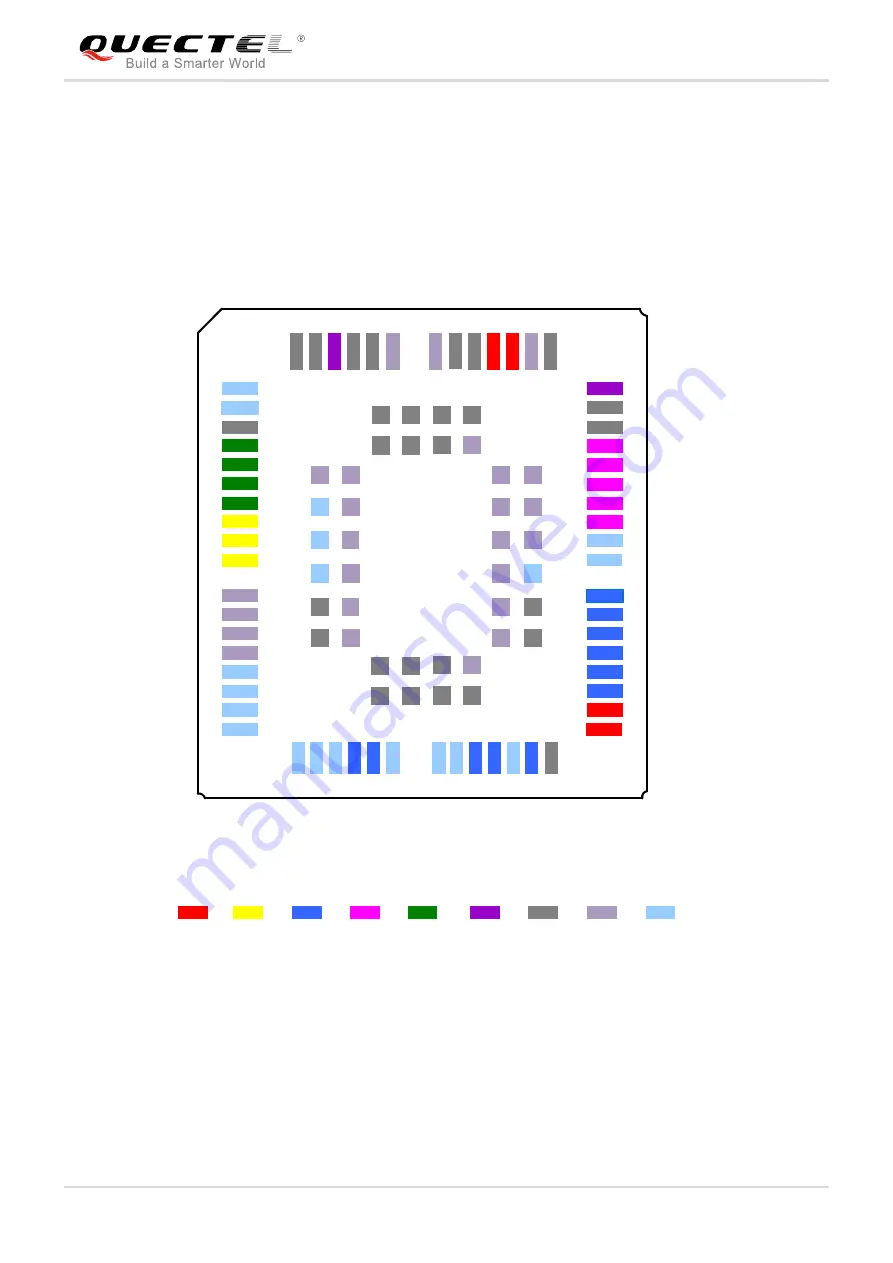

3.1. Pin Assignment

The following figure shows the pin assignment of BG95.

PSM_IND*

PCM_SYNC*

PCM_CLK*

PCM_IN*

PCM_OUT*

RESERVED

RESERVED

PWRKEY

2)

GPIO16

RESET_N

3)

W_DISABLE# *

1

2

3

4

5

6

7

11

12

13

14

15

17

50

51

52

53

54

55

58

59

60

61

62

USB_DM

AP

_R

E

A

D

Y

*

ST

AT

U

S

NE

T

L

IG

HT

DB

G

_RX

D

DB

G_

T

X

D

AD

C

0

1)

GP

IO

2

5

GP

IO

2

6

GN

S

S

_U

A

R

T

_T

X

D

G

N

SS

_U

AR

T

_R

X

D

VD

D

_EX

T

DT

R

GN

D

USIM_CLK

USIM_DATA

USIM_RST

USIM_VDD

RI

DCD

CTS

TXD

RXD

VBAT_BB

VBAT_BB

USIM_GND

GND

RE

S

E

RV

E

D

31

29

28

27

26

23

22

21

20

19

10

9

USB_DP

USB_VBUS

ADC1

1)

GND

RESERVED

RESERVED

RTS

I2C_SCL*

I2C_SDA*

8

49

48

47

46

45

44

43

40

41

42

39

38

37

36

35

34

33

24

57

56

GN

D

GN

D

AN

T

_M

A

IN

GN

D

GN

D

VB

A

T

_R

F

VB

AT

_R

F

GN

D

GN

D

ANT_GNSS

RE

S

E

RV

E

D

GN

D

USIM_PRESENCE*

63

64

65

66

67

68

83

84

85

86

87

88

98

97

96

95

94

93

78

77

76

75

74

73

91

92

89

90

71

72

69

70

80

79

82

81

100

99

102

101

POWER

USB

UART

(U)SIM

OTHERS

GND

RESERVED

PCM

ANT

RE

S

E

RV

E

D

18

GPIO64

16

25

32

USB_BOOT

65

GPIO65

GPIO66

30

Figure 2: Pin Assignment (Top View)