LTE-A Module Series

EG12 Hardware Design

EG12_Hardware_Design 52 / 97

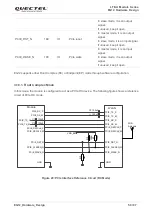

Table 17: Parameters of SPI Interface Timing

"*" means under development

3.13. PCM and I2C Interfaces

EG12 supports audio communication via Pulse Code Modulation (PCM) digital interface and I2C

interfaces. The PCM interface supports the following modes:

Primary mode (short frame synchronization, works as both master and slave)

Auxiliary mode (long frame synchronization, works as master only)

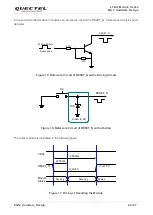

In primary mode, the data is sampled on the falling edge of the PCM_CLK and transmitted on the rising

edge. The PCM_SYNC falling edge represents the MSB. In this mode, PCM interface supports 256kHz,

512kHz, 1024kHz or 2048kHz PCM_CLK at 8kHz PCM_SYNC, and also supports 4096kHz PCM_CLK at

16kHz PCM_SYNC.

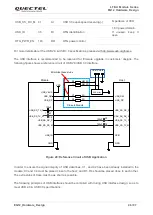

In auxiliary mode, the data is sampled on the falling edge of the PCM_CLK and transmitted on the rising

edge. The PCM_SYNC rising edge represents the MSB. In this mode, PCM interface operates with a

256kHz PCM_CLK and an 8kHz, 50% duty cycle PCM_SYNC only.

EG12 supports 16-bit linear data format. The following figures show the

primary mode’s timing

relationship with 8kHz PCM_SYNC and 2048kHz PCM_CLK, as well as

the auxiliary mode’s timing

relationship with 8kHz PCM_SYNC and 256kHz PCM_CLK.

Parameter

Description

Min.

Typ.

Max.

Unit

T

SPI clock period

20.0

-

-

ns

t(ch)

SPI clock high level time

9.0

-

-

ns

t(cl)

SPI clock low level time

9.0

-

-

ns

t(mov)

SPI master data output valid time

-5.0

-

5.0

ns

t(mis)

SPI master data input setup time

5.0

-

-

ns

t(mih)

SPI master data input hold time

1.0

-

-

ns

NOTE