LTE-A Module Series

EG12 Hardware Design

EG12_Hardware_Design 57 / 97

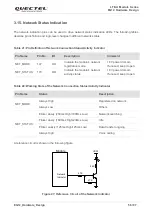

3.16. Status

The STATUS pin is set as the module status indicator. It outputs high level voltage when the module is

turned on.

The following table describes pin definition of STATUS.

Table 23: Pin Definition of STATUS

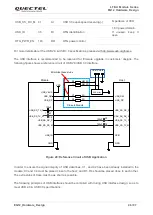

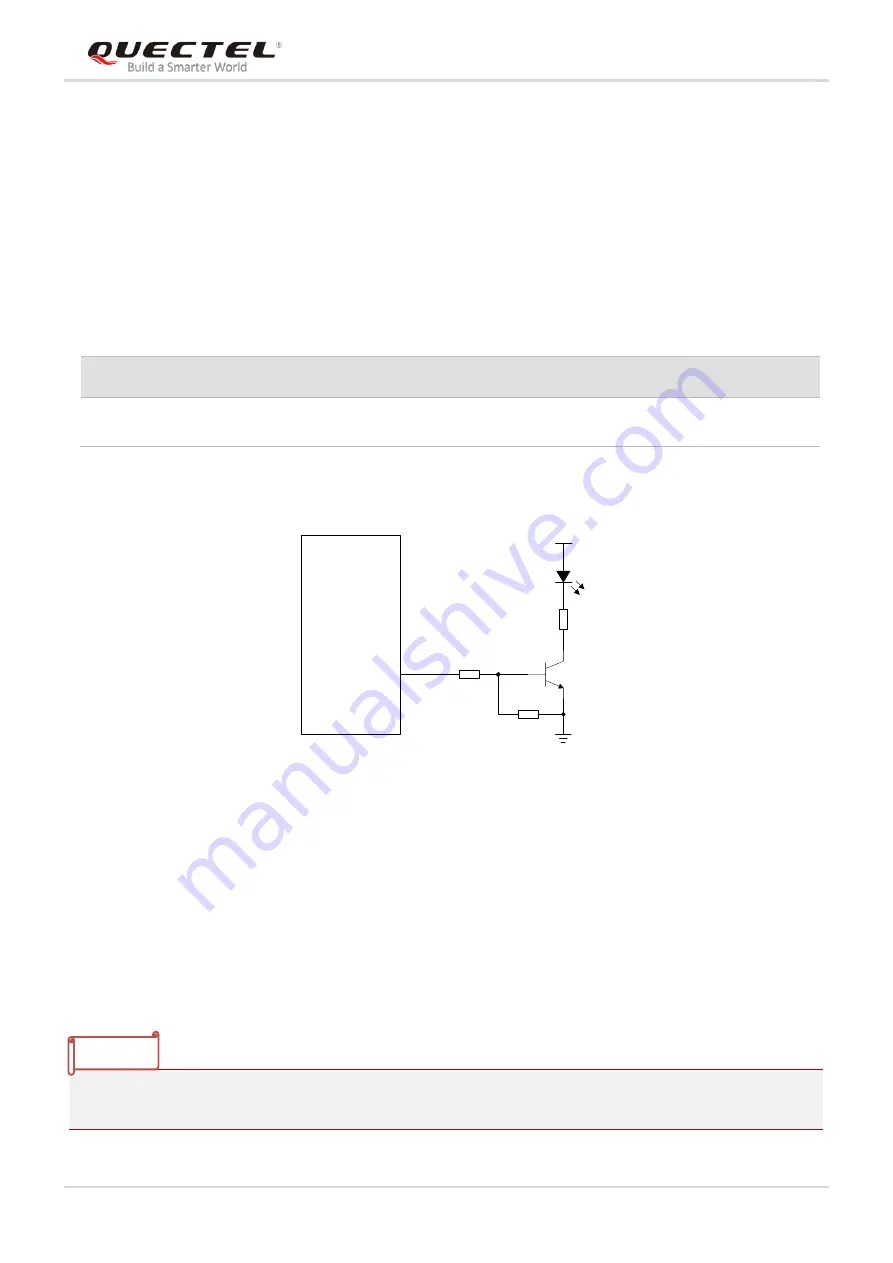

A reference circuit is shown as below.

4.7K

47K

VBAT

2.2K

Module

STATUS

Figure 28: Reference Circuits of STATUS

3.17. Behavior of the RI

AT+QCFG="risignaltype","physical"

command can be executed to configure RI behavior.

No matter on which port a URC is presented, the URC will trigger the behavior of RI pin.

The URC can be output from UART port, USB AT port and USB modem port by executing

AT+QURCCFG

command. The default port is USB AT port.

Pin Name Pin No.

I/O

Description

Comment

STATUS

171

DO

Indicate the module

’s operation status

1.8V power domain

If unused, keep it open.

NOTE