LTE-A Module Series

EG12 Hardware Design

EG12_Hardware_Design 51 / 97

3.12. SPI Interface*

EG12 provides one SPI interface multiplexed from BT UART interface. The interface only supports master

mode with a maximum clock frequency up to 50MHz.

The following table shows the pin definition of SPI interface.

Table 16: Pin Definition of SPI Interface

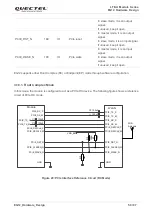

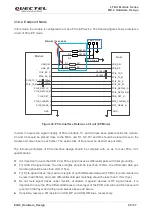

The following figure shows the timing relationship of SPI interface.

SPI_CS_N

SPI_CLK

SPI_MOSI

MSB

1

2

SPI_MISO

3

T

t(mov)

4

t(mis)

t(mih)

t(ch) t(cl)

Figure 23: Timing of SPI Interface

The related parameters of SPI timing are shown in the following table.

Pin Name

Pin No.

I/O

Description

Comment

BT_TXD

163

DO

Can be multiplexed into SPI_MOSI.

1.8V power domain

BT_CTS

164

DO

Can be multiplexed into SPI_CLK.

BT_RXD

165

DI

Can be multiplexed into SPI_MISO.

BT_RTS

166

DI

Can be multiplexed into SPI_CS.