PROJECT

TITLE

Lorry XU

Woody WU

CHECKED BY

DRAWN BY

OF

A

6

5

4

3

2

1

SHEET

A

B

C

D

1

2

3

4

5

6

D

C

B

Quectel Wireless Solutions

SIZE

VER

14

9

1.0

DATE

2019/12/5

EG21-G

A2

Reference Design

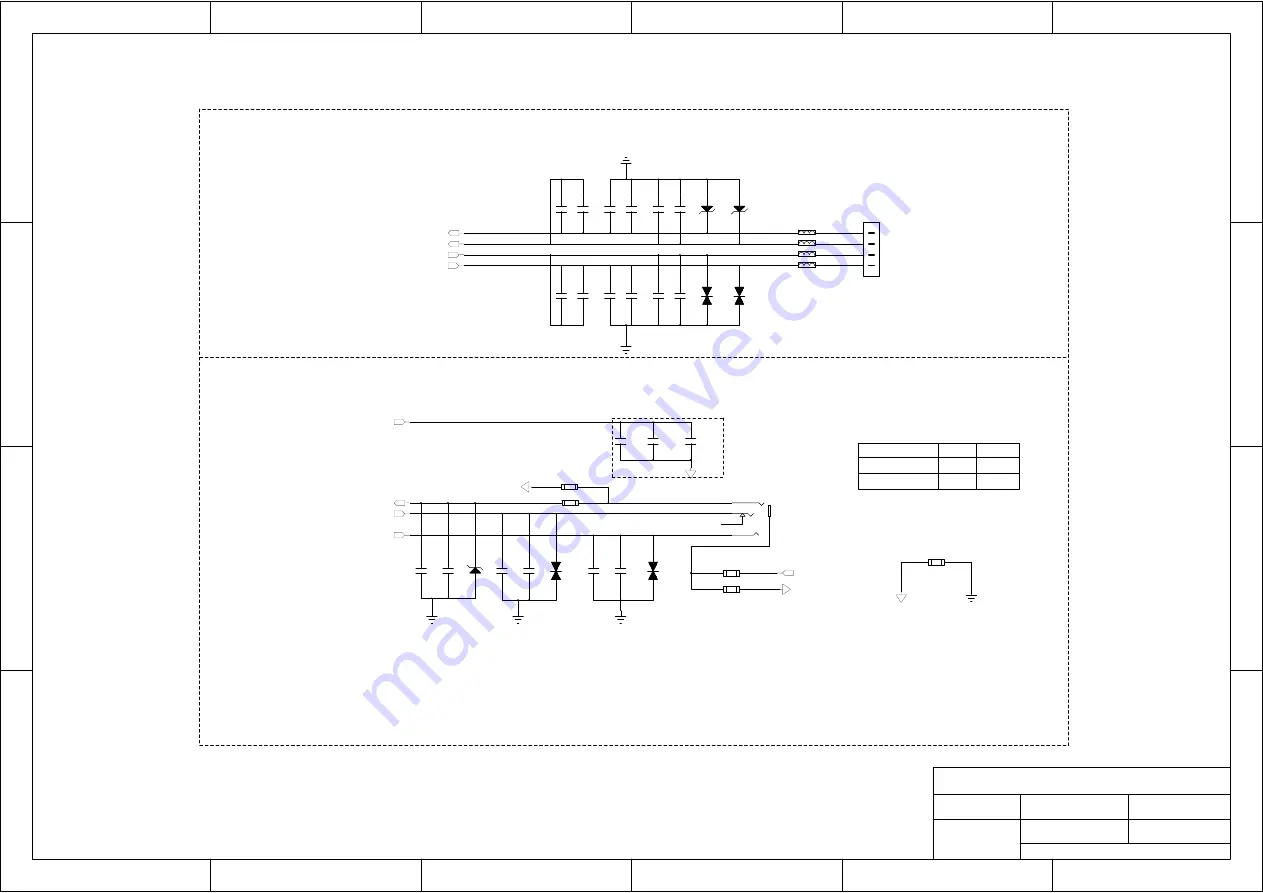

Handset Application

Earphone Application

Close to earphone interface

Notes:

Audio Interfaces

CTIA OMTP

R0702/R0705

R0701/R0704

M

M

NM

NM

1. The analog output only drives earphone and headset. For larger power loads such as speakers, an audio power amplifier should be added in the design.

2. In handset application, both the MIC and SPK signal traces need to be routed as differential pairs.

3. In earphone application, the MIC signal traces need to be routed as differential pairs.

4. All MIC and SPK signal traces should be routed with total grounding and far away from noise such as clock and DC-DC signals, etc.

5. ALC5616 and TLV320AIC3104 cannot be used simultaneously in audio codec design.

4

1

3

2

J0701

D

0701

ESD9X5.0ST5G

D

0702

C

0702

33pF

C

0704

33pF

C

0705

10pF

C

0703

10pF

C

0706

33pF

C

0701

10pF

C

0709

10pF

C

0710

33pF

C

0711

10pF

C

0712

33pF

C

0708

33pF

C

0707

10pF

C0713

10pF

C0714

33pF

C0715

4.7μF

D

0703

PESD5V0S1BL

D

0704

R0703

0R

R-0805

1

2

3

4

5

J0702

C

0716

10pF

C

0717

33pF

D

0705

ESD

9X5.0ST5G

R0702

NM_0R

R0701

0R

R0704

0R

R0705

NM_0R

D

0706

PESD5V0S1BL

C

0718

10pF

C

0719

33pF

D

0707

PESD5V0S1BL

C

0720

10pF

C

0721

33pF

F0701

0R

F0702

0R

F0704

0R

F0703

0R

[7,8]

SPK_P

[7,8,9] MIC_P

[7,8,9] MIC_N

[7,8,9] MIC_N

[7,8]

SPK_N

[7,8]

SPK_R

[7,8]

SPK_L

[7,8,9] MIC_P

[7,8,9]

MIC_P