Instruction Reference Manual

65

Description

These instructions are used to access 20-bit addresses. In all cases, the four most significant bits of the 20-bit

address (bits 19 through 16) are defined as the four least significant bits of the Accumulator (bits 3 though 0).

The LDP instructions bypass the MMU’s address translation unit for direct access to the 20-bit memory

address space. These instructions are implemented for the Rabbit and are not available for the Z180.

•

LDP HL,(HL):

Loads the register L with the data whose 16 least significant bits of its 20-bit

address are the data in paired register HL, and then loads the register H with the data in the fol-

lowing 20-bit address.

•

LDP HL,(IX):

Loads the register L with the data whose 16 least significant bits of its 20-bit

address are the data in index register IX, and then loads the register H with the data in the follow-

ing 20-bit address.

•

LDP HL,(IY):

Loads the register L with the data whose 16 least significant bits of its 20-bit

address are the data in index register IY, and then loads the register H with the data in the follow-

ing 20-bit address.

Note that the LDP instructions wrap around on a 64K page boundary. Since the LDP instruction operates on

two-byte values, the second byte will wrap around and be written at the start of the page if you try to read or

write across a page boundary. Thus, if you fetch or store at address 0xn,0xFFFF, you will get the bytes

located at 0xn, 0xFFFF and 0xn,0x0000 instead of 0xn,0xFFFF and 0x(n+1),0x0000 as you might expect.

Therefore, do not use LDP at any physical address ending in 0xFFFF.

LDP HL,(HL)

LDP HL,(IX)

LDP HL,(IY)

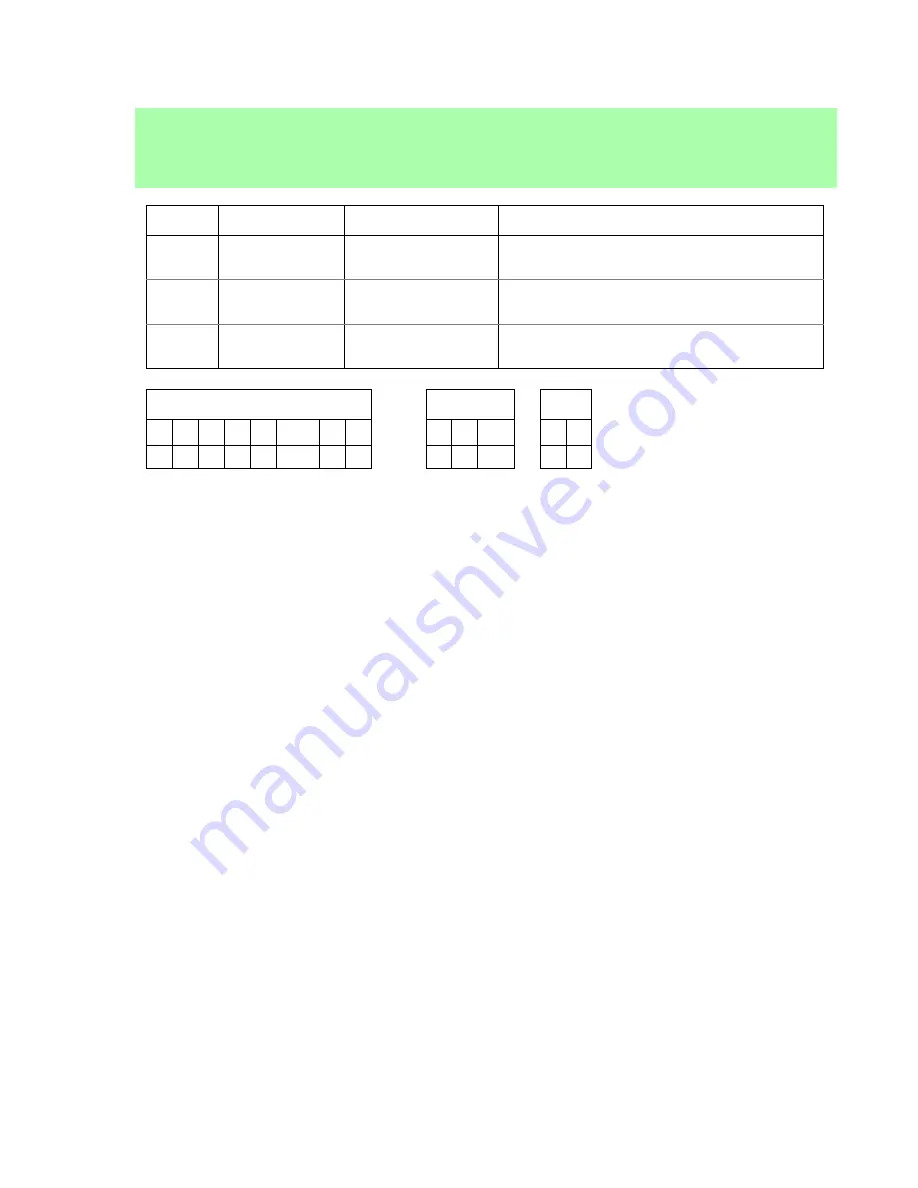

Opcode

Instruction

Clocks

Operation

ED 6C

LDP HL,(HL)

10 (2,2,2,2,2)

L = (HL); H = (HL + 1).

(Addr[19:16] = A[3:0])

DD 6C

LDP HL,(IX)

10 (2,2,2,2,2)

L = (IX); H = (IX + 1).

(Addr[19:16] = A[3:0])

FD 6C

LDP HL,(IY)

10 (2,2,2,2,2)

L = (IY); H = (IY + 1).

(Addr[19:16] = A[3:0])

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

-

-

-

-

Summary of Contents for 2000

Page 2: ...ii Rabbit 2000 3000 Microprocessor...

Page 4: ...iv Rabbit 2000 Microprocessor...

Page 16: ...12 Rabbit 2000 3000 Microprocessor...

Page 112: ...108 Rabbit 2000 3000 Microprocessor...

Page 120: ...ii Rabbit 2000 3000 Microprocessor...