Instruction Reference Manual

105

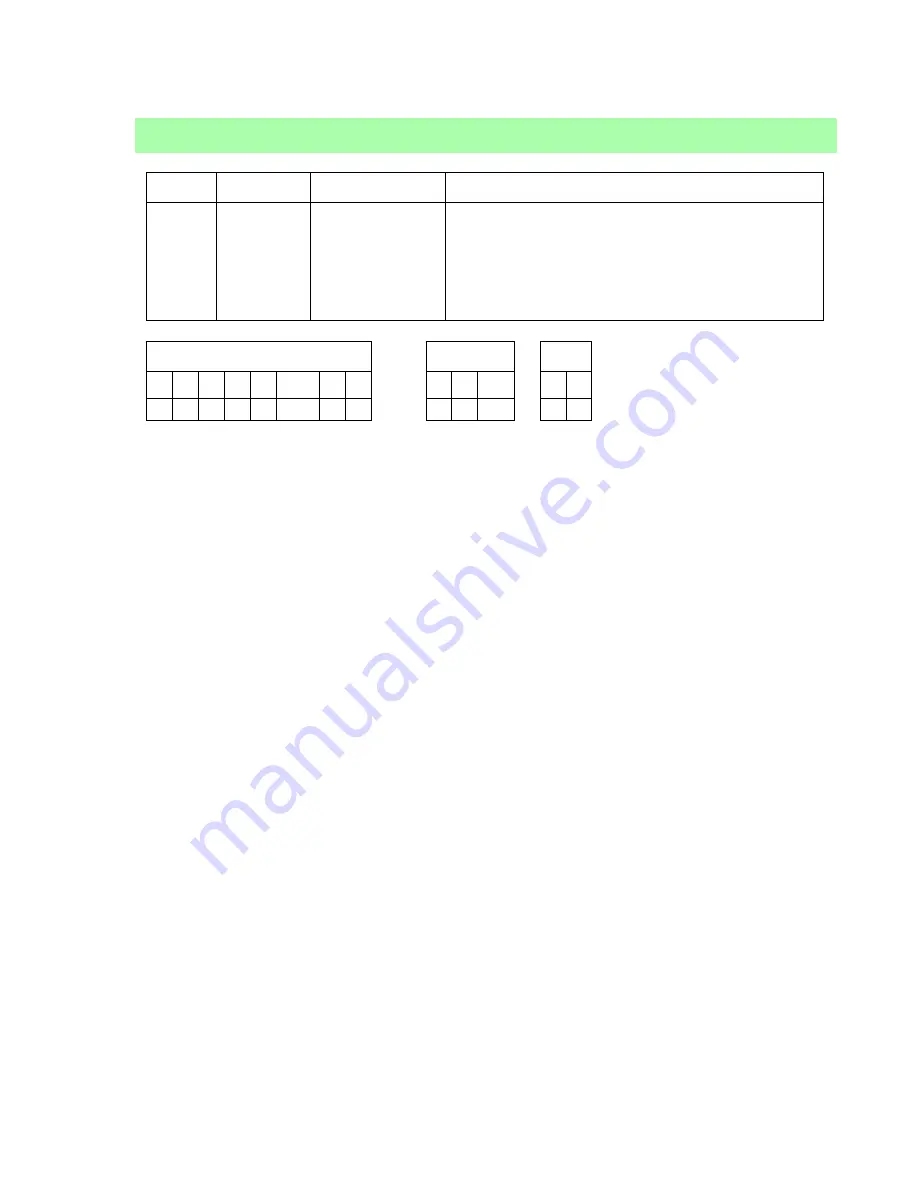

Description

Loads the low order byte of the zz (any of AF, BC, DE, or HL) with the data at the memory address in SP

then loads the high order byte of zz with the data at the memory address immediately following the one held

in SP. SP is then incremented twice.

POP

zz

Opcode

Instruction

Clocks

Operation

——

F1

C1

D1

E1

POP

zz

POP AF

POP BC

POP DE

POP HL

7 (2,1,2,2)

7 (2,1,2,2)

7 (2,1,2,2)

7 (2,1,2,2)

7 (2,1,2,2)

zz

(low)

= (SP);

zz

(high)

= (SP + 1);

SP = SP + 2

F = (SP); A = (SP + 1); SP = SP + 2

C = (SP); B = (SP + 1); SP = SP + 2

E = (SP); D = (SP + 1); SP = SP + 2

L = (SP); H = (SP + 1); SP = SP + 2

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

-

-

-

-

•

Summary of Contents for 2000

Page 2: ...ii Rabbit 2000 3000 Microprocessor...

Page 4: ...iv Rabbit 2000 Microprocessor...

Page 16: ...12 Rabbit 2000 3000 Microprocessor...

Page 164: ...160 Instruction Reference Manual...