156

Instruction Reference Manual

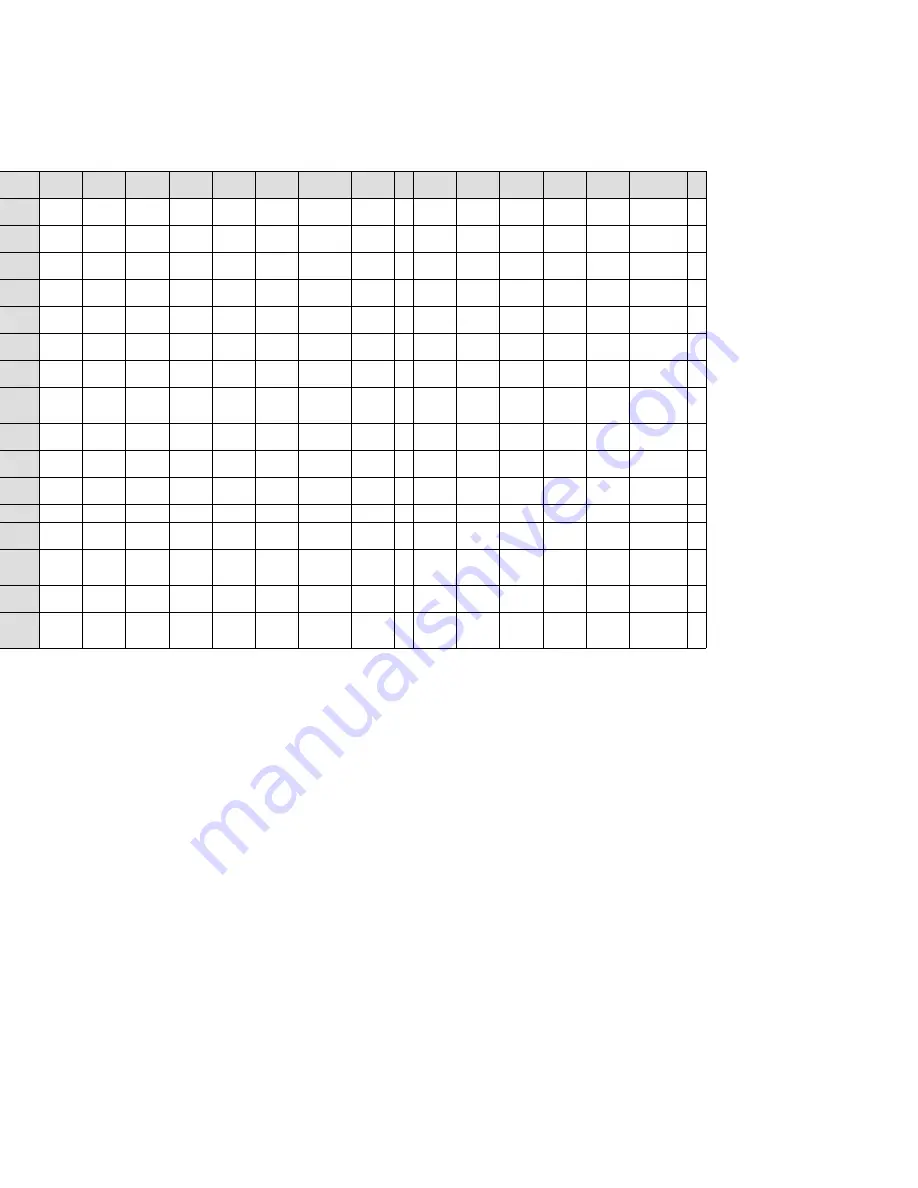

Table 4: FD Page

\LSB

MSB\

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0

ADD

IY,BC

1

ADD

IY,DE

2

LD

IY,mn

LD

(mn),IY

INC

IY

ADD

IY,IY

LD

IY,(mn)

DEC

IY

3

INC

(IY+d)

DEC

(IY+d)

LD

(IY+d),n

ADD

IX,SP

4

LD

B,(IY+d)

LD

C,(IY+d)

5

LD

D,(IY+d)

LD

E,(IY+d)

6

LDP

(IY),HL

LDP

(mn),IY

LD

H,(IY+d)

LDP

HL,(IY)

LDP

IY,(mn)

LD

L,(IY+d)

7

LD

(IY+d),

B

LD

(IY+d),

C

LD

(IY+d),

D

LD

(IY+d),

E

LD

(IY+d),

H

LD

(IY+d),

L

LD

(IY+d),

A

LD

HL,IY

LD

IY,HL

LD

A,(IY+d)

8

ADD

A,(IY+d)

ADC

A,(IY+d)

9

SUB

(IY+d)

SBC

A,(IY+d)

A

AND

(IY+d)

XOR (IY+d)

B

OR (IY+d)

CP

(IY+d)

C

LD IY,

(SP+n)

esc

BOOL

IY

D

LD

(SP+n),

IY

AND

IY,DE

E

POP

IY

EX

(SP),IY

LD HL,

(IY+d)

PUSH

IY

JP

(IY)

OR

IY,DE

F

LD

(IY+d),

HL

LD

SP,IY

RR

IY

Summary of Contents for 2000

Page 2: ...ii Rabbit 2000 3000 Microprocessor...

Page 4: ...iv Rabbit 2000 Microprocessor...

Page 16: ...12 Rabbit 2000 3000 Microprocessor...

Page 164: ...160 Instruction Reference Manual...