Instruction Reference Manual

23

Description

This is an instruction prefix. Causes the instruction immediately following to affect the alternate flags, or use

the alternate registers for the destination of the data, or both. For some instructions ALTD causes special

alternate register uses, unique to that instruction.

Example

The instruction

ALTD ADD HL,DE

would add the data in DE to the data in HL and store the result in the alternate register HL'.

The instructions

ALTD LD DE,BC

and

LD DE',BC

both load the data in BC into the alternate register DE'.

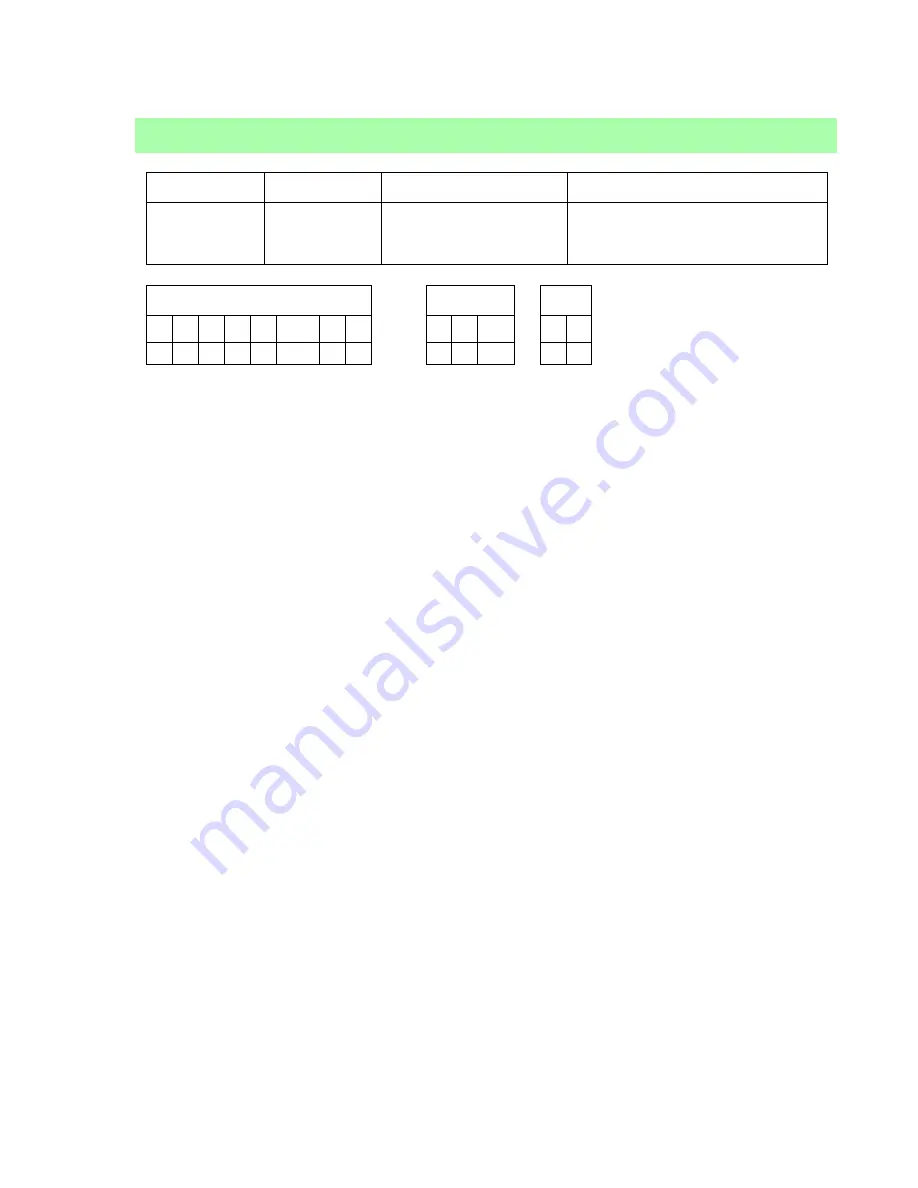

ALTD

Opcode

Instruction

Clocks

Operation

76

ALTD

2

[Sets alternate register

destination for following

instruction.]

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

-

-

-

-

Summary of Contents for 2000

Page 2: ...ii Rabbit 2000 3000 Microprocessor...

Page 4: ...iv Rabbit 2000 Microprocessor...

Page 16: ...12 Rabbit 2000 3000 Microprocessor...

Page 164: ...160 Instruction Reference Manual...